SI/PI-Database

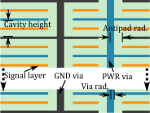

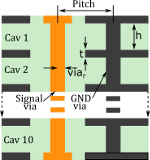

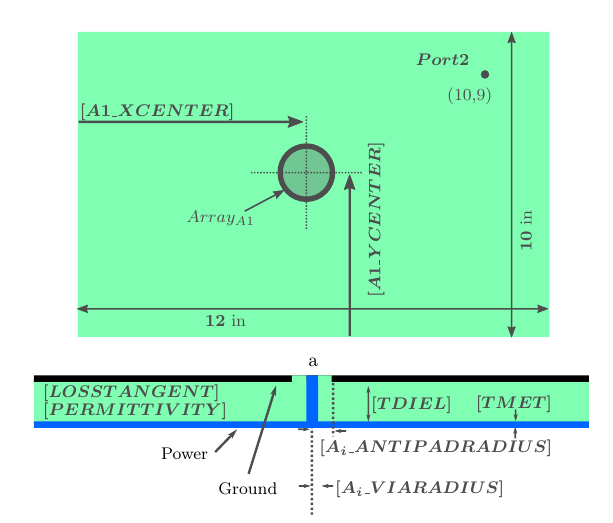

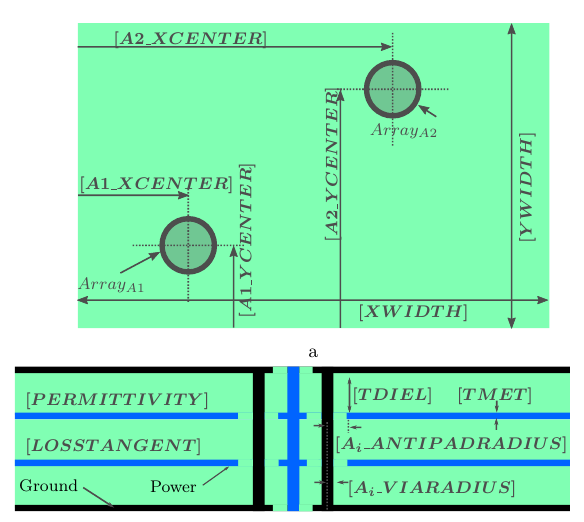

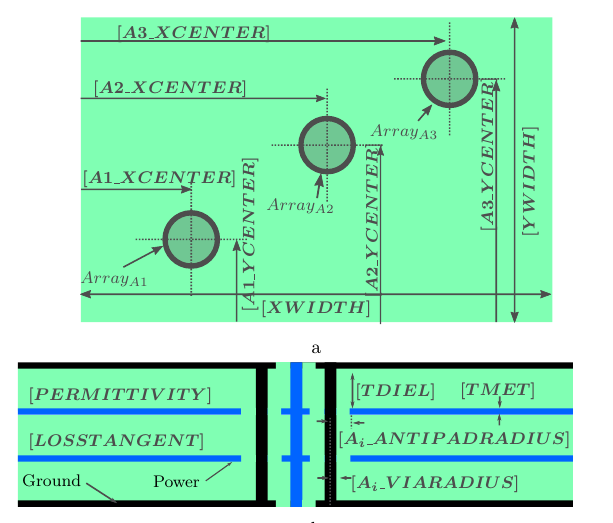

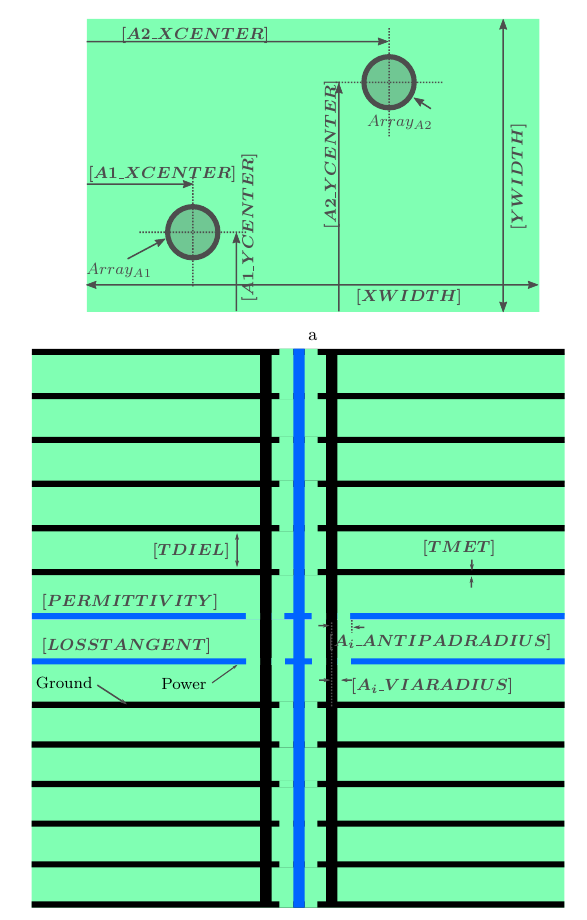

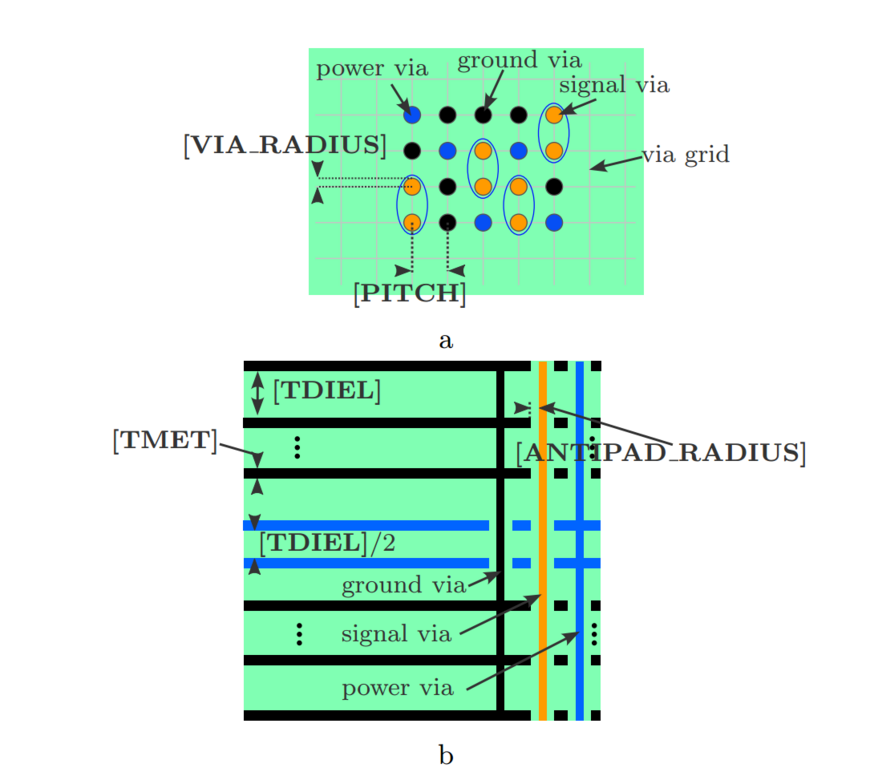

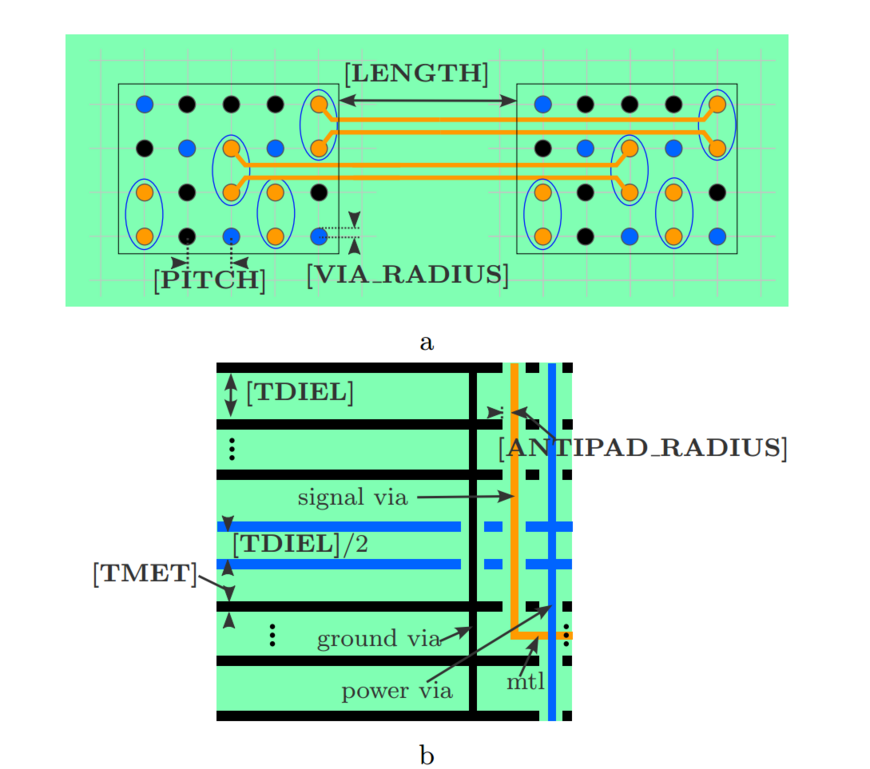

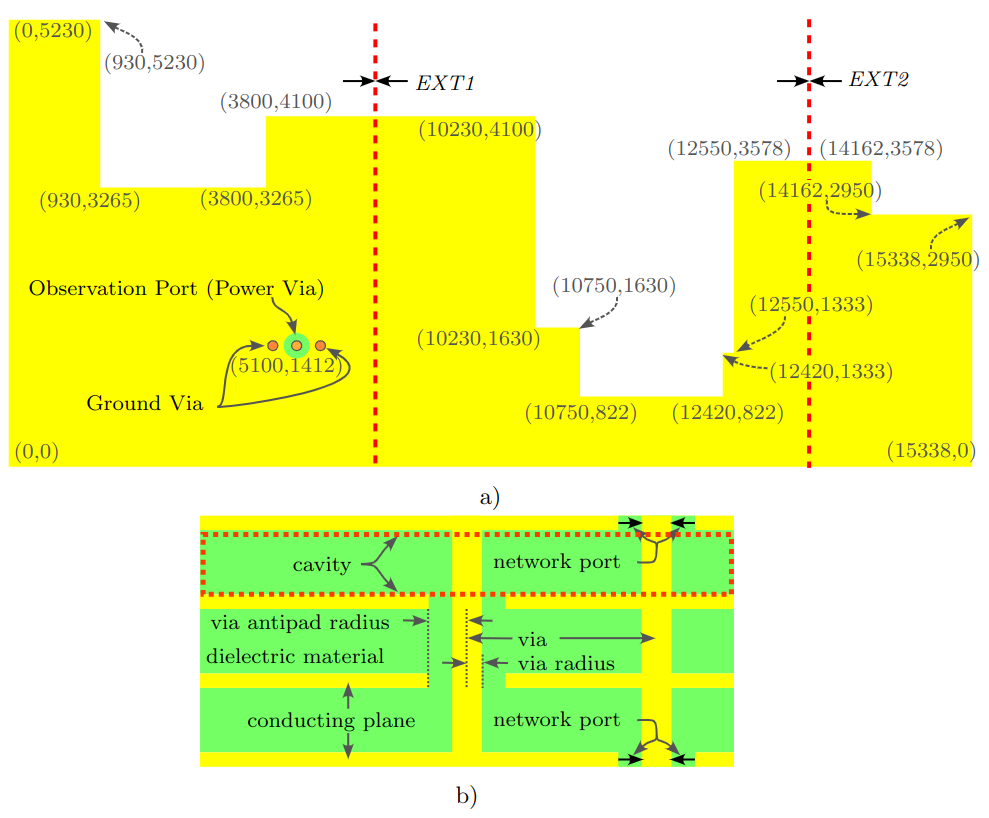

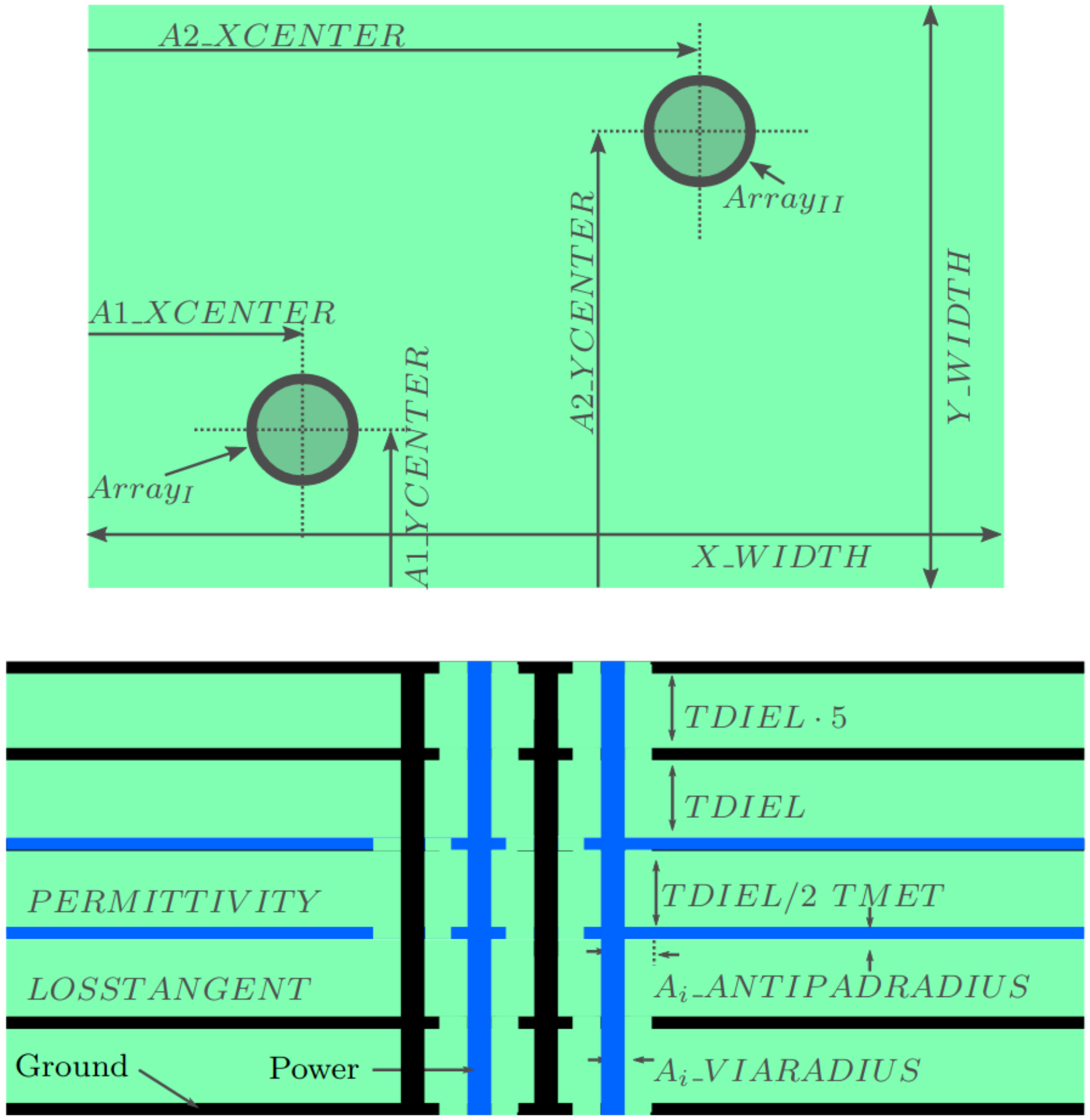

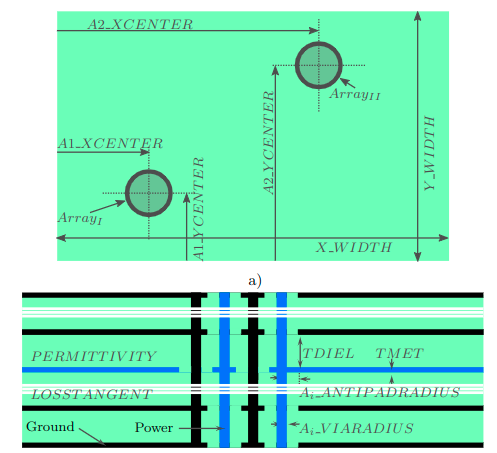

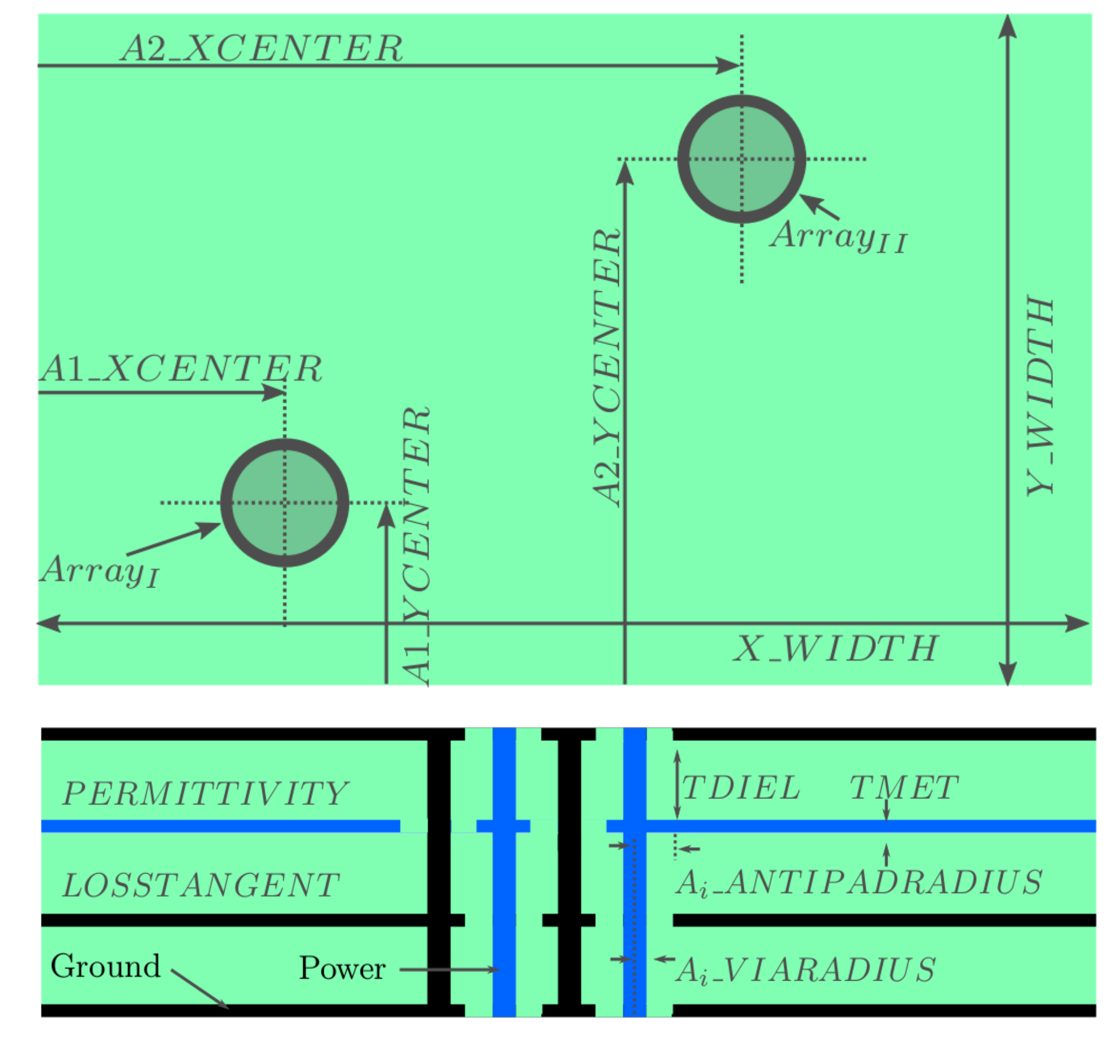

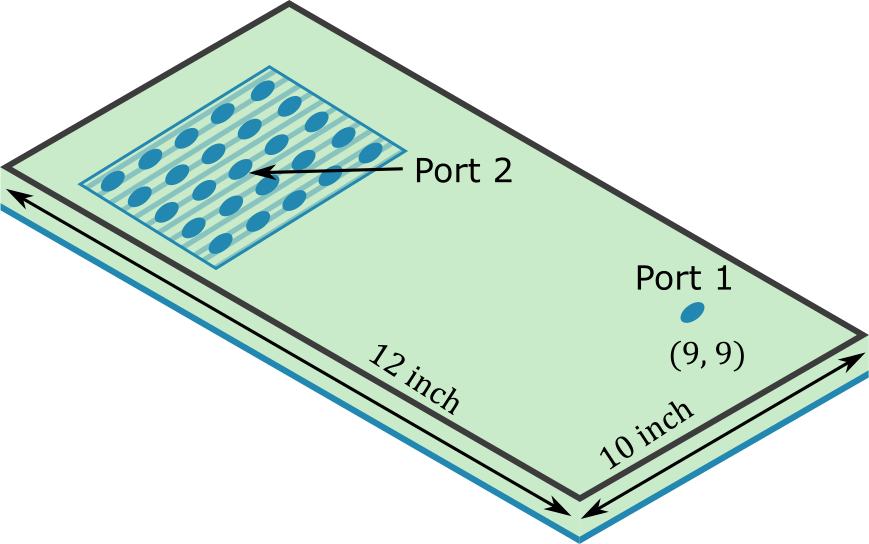

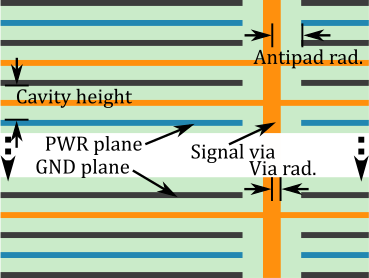

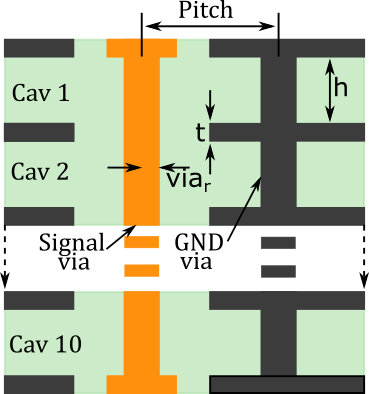

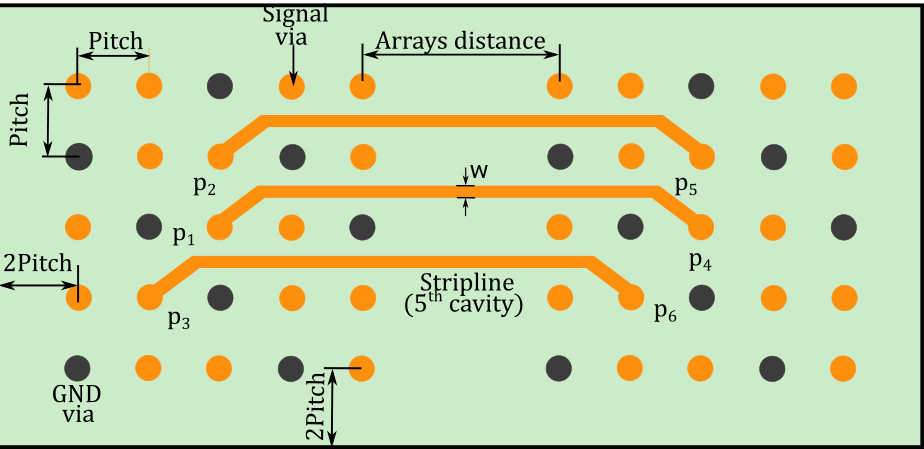

The SI/PI-Database is a collection of printed circuit board (PCB) based structures which represent different electromagnetic aspects for signal integrity and power integrity applications. The structures have different components and interconnecting elements e.g. via-arrays, different planes or dimension. Each structures contains many variations of geometry and material parameters and their respective simulation results. All structures were simulated with a physics-based approach, developed by the Institut für Theoretische Elektrotechnik, and cross validated with a full-wave solver.

Publications related to the Physics-Based Approach of the institute:

Please fill out the contact form to receive the link for the download file.

To get access to the data please fill out the contact form. You will receive a download link by the entered e-mail address. The zip-archive contains multiple files.First, a description of the structure with explanation regarding the parameter variations. Second, a .csv file which gives an overview over all parameter variations along with classification labels and the simulation index (simu_index). Last, the scattering parameters for the according simulation file is found by the (simu_index) . For each parameter variation a touchstone file simu_index.sNp is available.

Any usage of the data of the SI/PI-Database has to be referenced to the following article: