# 5x5 Via-Array on 10 Cavity PCB

Morten Schierholz {morten.schierholz@tuhh.de}

Institut für Theoretische Elektrotechnik, Hamburg University of Technology (TUHH), Hamburg, Germany

December 20, 2020

#### I. DESCRIPTION

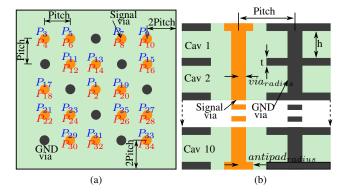

The  $5 \times 5$  via array is located on a 10 cavity printed circuit board (PCB), as shown in Fig 2. The connectivity of GND and signal vias is shown in Fig 2 (a), with a via ratio of 2 : 1 for signal and GND, respectively. At each via two ports are placed one at the top (odd numbers) of the PCB and one at the bottom (even numbers) . A more thoroughly description is given in [1]. This array is used for a high density IC package. All planes of the stackup are connected by GND vias. The radius of the via barrel is smaller than the radius of the via pads on top and bottom of the stackup, as shown in Fig. 2 (a). All pad of the signal vias are exactly as the via radius (pad\_radius-2.5 mil). For the top most and bottom most plane (GND planes) the pad radius is pad\_radius.

#### II. MODELING TOOL

All simulations have been carried out with a physics-based (PB) approach [2]–[4]. A demo version of the tool can be accessed over *www.tet.tuhh.de*. All information regarding the setup are described in the following.

### III. PARAMETER

If a value is given in the tables the parameter is not altered during the simulations. On the other hand if the value is varied the according entry of the < parameter.csv > file is given.

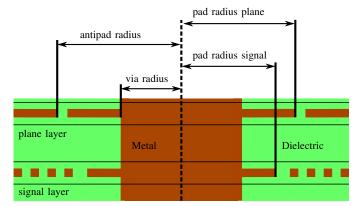

# A. Via Model

The dimensions of the vias used in the structure shown in Fig. 2 are given in Fig. 1. All vias are based on this model. For the dielectric material (Dielectric) the rel. permittivity ( $\varepsilon_r$ ) and the loss tangent (tan  $\delta$ ) are given. For the conductive material (Metal) the conductivity ( $\sigma$ ) is given. An overview is given in Tab. I.

Table I: Overview of the parameters used in the via model, as shown in Fig. 1

| Parameter         | Value              |

|-------------------|--------------------|

| via radius        | pad_radius-2.5 mil |

| antipad radius    | antipad_radius     |

| pad radius plane  | pad_radius         |

| pad radius signal | pad_radius-2.5 mil |

Fig. 1: Via model used for all vias of the structure. If the radius values are not given the  $via_{radius}$  is used for  $pad_{radius\_plane}$ , and  $pad_{radius\_sgnal}$ .

Fig. 2: (a) is the top view in the 5x5 via-array, (b) is the stackup. GND vias are connected to all ground planes. The ports are placed on top and bottom of the PCB. Top ports are blue (odd numbers), bottom ports are red (even numbers).

### B. Materials

Two different materials were used, the material for the metal e.g. planes, striplines, vias, pads, and the material for the dielectric e.g. cavity filling, antipad. The metal requires two parameter conductivity ( $\sigma$ ) and rel. permeability ( $\mu_r$ ). The dielectric has the rel. permittivity ( $\varepsilon_r$ ) and the loss tangent (tan  $\delta$ ). An overview is given in Tab. II.

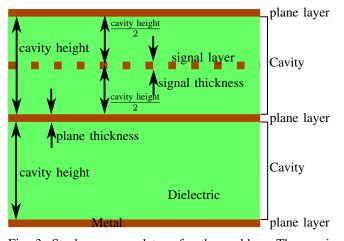

# C. Stackup

For the stackup general parameters are introduced. If not stated differently in the description the naming refers to all cavities of the stackup. One cavity is defined by the enclosed dielectric material by two planes, as shown in Fig. 3. Signal Table II: Overview of the material parameters used in the structure.

| Parameter       | Value                         |

|-----------------|-------------------------------|

| σ               | $1 \times 10^{30} \text{S/m}$ |

| $\mu_r$         | 1                             |

| $\varepsilon_r$ | epsilon_r                     |

| $tan \delta$    | loss_tangent                  |

Fig. 3: Stackup nomenclature for the problem. The naming refers to all cavities unless stated differently in the description.

layers are defined in the middle of the cavity. The cavity height is the distance between two plane layers (here diel\_height).

Table III: Overview of the parameters related to the stackup used in the PCB.

| Parameter        | Value           |

|------------------|-----------------|

| cavity height    | diel_height     |

| plane thickness  | plane_thickness |

| signal thickness | plane_thickness |

#### D. File <parameter.csv>

The file < parameter.csv > has all necessary information for the setup of the geometry and parameter variations. The columns are:

- index

- simuIndex

- antipad\_radius

- pad\_radius

- via\_pitch

- diel\_height (h)

- plane\_thickness

- epsilon\_r

- loss\_tangent

Index is the row in the  $\langle parameter.csv \rangle$ , diel\_height is the distance between the two metal planes, epsilon\_r is the relative permittivity ( $\varepsilon_r$ ) of the dielectric between the power and ground planes, loss\_tangent is  $tan(\delta)$  of the dielectric, plane\_thickness is thickness of plane layers, via\_pitch is the distance between vias in the array, pad\_radius is the radius of the via pad on top and bottom of the PCB, antipad\_radius is the radius of the cutout around a via, simuIndex is the simulation index (<index>) to find the simulation results.

# IV. PUBLICATIONS

This structure was used in [1].

#### REFERENCES

- [1] A. S. Masís, A. Carmona-Cruz, M. Schierholz, X. Duan, K. Roys, C. Yang, R. Rimolo-Donadio, and C. Schuster, "Generation of Via Interconnect Classification Models with Feed-Forward Neural Networks assisted by Genetic Algorithms," to be submitted to 2021 IEEE 25th Workshop on Signal and Power Integrity (SPI), Jul. 2021.

- [2] R. Rimolo-Donadio, X. Gu, Y. Kwark, M. Ritter, B. Archambeault, F. de Paulis, Y. Zhang, J. Fan, H.-D. Brüns, and C. Schuster, "Physics-Based Via and Trace Models for Efficient Link Simulation on Multilayer Structures Up to 40 GHz," *IEEE Transactions Microwave Theory and Techniques*, vol. 57, no. 8, pp. 2072–2083, Aug. 2009.

- [3] S. Müller, X. Duan, M. Kotzev, Y.-J. Zhang, J. Fan, X. Gu, Y. H. Kwark, R. Rimolo-Donadio, H.-D. Brüns, and C. Schuster, "Accuracy of Physics-Based Via Models for Simulation of Dense Via Arrays," *IEEE Transactions on Electromagnetic Compatibility*, vol. 54, no. 5, pp. 1125–1136, Oct. 2012. [Online]. Available: https://doi.org/10.1109/temc.2012.2192123

- [4] S. Müller, F. Happ, X. Duan, R. Rimolo-Donadio, H.-D. Bruns, and C. Schuster, "Complete Modeling of Large Via Constellations in Multilayer Printed Circuit Boards," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 3, no. 3, pp. 489–499, Mar. 2013. [Online]. Available: https://doi.org/10.1109/tcpmt.2012.2234211