Entwicklung einer automatisierten Speicherung von Simulationsdaten aus Numerischen Simulationstools auf Grundlage von OpenBIS

Tommy Weber, Wissenschaftliche Hilfskraft, 01.06.2023-30.11.2023

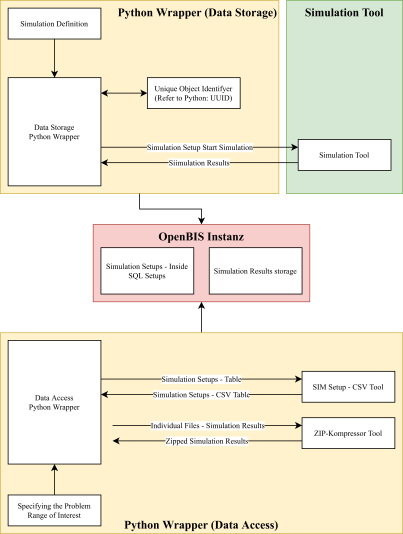

Die Aufbewahrung und Dokumentation von Simulationsdaten ist fundamental im Zusammenhang mit Anwendungen des maschinellen Lernens. Aus diesem Grund, wird eine automatisierte Speicherung der Simulationsdaten mit Hilfe eines Datenbanksystems angestrebt. In der ersten Phase sollen zwei Systeme miteinander kombiniert werden.

- Speichersystem (Evtl. OpenBIS, https://openbis.ch/), inkl. Datenspeicher, Versionierung, und SQL Datenbank

- Anbindung an interne Simulationstools des TET Instituts (https://www.tet.tuhh.de/en/concept-2/), in Form eine Python Wrappers. Primär-Fokus ist auf der Anbindung von CONMLS, grundsätzlich ist eine spätere Erweiterung auf Beispielsweise CONCEPT-II, CONMTL zu berücksichtigen.

Das Ergebnis der ersten Phase soll eine Umgebung sein, in der ein Experiment definiert werden kann. Ein Experiment, kann beispielsweise ein bestimmter Aufbau eines PCBs sein (Anzahl Lagen, Ports, Vias, …). Innerhalb dieses Experiments werden Simulationen definiert, die durchgeführt werden. Beispielsweise anhand eines bestimmten Samplings (Random, Latin Hypercube, …). Beim Ausführen der Simulationen werden diese, inkl. der Ergebnisse (Streuparameter im LYD.H5 Format) auf dem Speichersystem abgelegt. Später können die Ergebnisse, oder auch Simulationseinstellungen wieder abgerufen werden, von dem Speichersystem. Die genannten Funktionalitäten sollen im internen Institutsbetrieb zur Verfügung stehen, zum Abschluss von Phase 1.

Die zweite Phase soll die Möglichkeit des Zugriffs auf die vorhandenen Simulationsdaten auch von extern ermöglichen in einem begrenzten Umfang. Auswahl der Simulationsdaten ist möglich, es werden jedoch lediglich komprimierte ZIP-Ordner zur Verfügung gestellt, mit Simulationsergebnissen und Parametervariationen. Die Umsetzung dieser Phase wird nicht vollständig erfolgen, sondern zunächst mit der Konzeptphase enden.

Entwurf von High-Speed Interconnects für Gbps-Verbindungen im Automobilbereich

Die Entwicklung von Hochgeschwindigkeitsverbindungen für drahtgebundene Verbindungen in digitalen Systemen ist bereits seit mehreren Jahrzehnten ein etablierter Bereich der Forschung und Innovation. Im Gegensatz dazu haben sich Hochgeschwindigkeitsverbindungen in Kraftfahrzeugen erst in jüngster Zeit zu immer höheren Datenraten entwickelt. Dementsprechend wurden Modelle für Komponenten, die speziell für Verbindungen in Kraftfahrzeugen geeignet sind, bisher weder in großem Umfang erstellt oder validiert, noch wurde eine ausreichende Modell-Hardware-Korrelation hergestellt. Darüber hinaus müssen Hochgeschwindigkeitsverbindungen im Automobil strenge Anforderungen hinsichtlich der elektromagnetischen Verträglichkeit (EMV) erfüllen. Ziel dieses Projekts ist die Entwicklung von Hochgeschwindigkeits-Verbindungsmodellen, die in Automobilanwendungen auf Systemebene verwendet werden. Diese Modelle werden angepasst, um Leiterplatten (PCBs) zu analysieren, die in Automobilanwendungen in Kombination mit Montage- und Verbindungstechnologien verwendet werden. Sie geben einen Einblick in die Signalintegritätsleistung von Hochgeschwindigkeitsverbindungen in rauen Automobilumgebungsstandards, um ein funktionierendes System zu haben, das sowohl die elektrische Leistung als auch die Zuverlässigkeitsanforderungen erfüllt.

Finanzierung: Robert Bosch GmbH

Kontakt: Jose Enrique Hernandez Bonilla

Start Datum: 01.09.2022

Daten Getriebener Entwurf und Analyse von Hochgeschwindigkeits Verbindungen von Leiterplatten

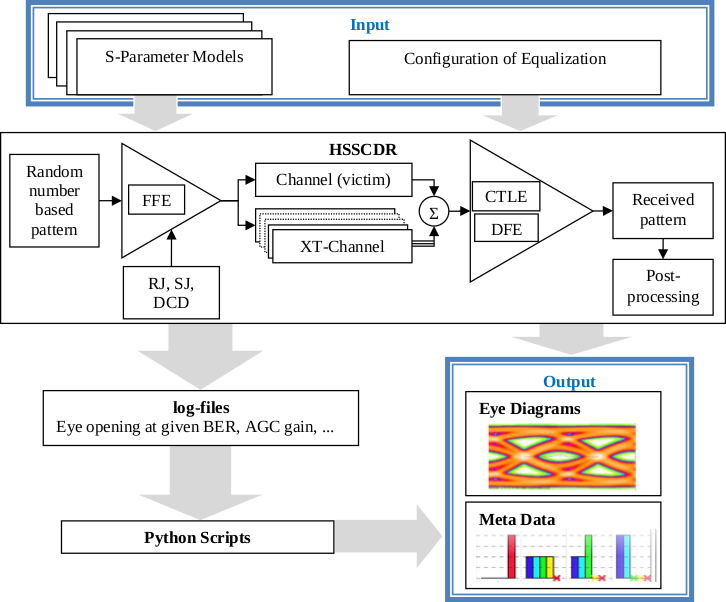

Durch den Ausbau von Informationsnetzen wie beispielsweise das industrielle Internet of Things (IoT) entsteht eine stets steigende Nachfrage nach Daten. Diese erzeugt in logischer Folge eine Nachfrage nach Datenerzeugung, -verarbeitung, -speicherung und dem Datentransport zwischen diesen Schritten. In diesem Projekt werden Möglichkeiten untersucht, wie ein schneller Datentransport gewährleistet werden kann. Ziel ist es dabei Methoden des maschinellen Lernens (ML) zu nutzen, um den Entwurfsprozess für Hochgeschwindigkeits Verbindungen zu beschleunigen. Das Hauptaugenmerk liegt dabei auf der Struktur der Leiterplatte, jedoch werden dabei auch die Effekte von Line Coding und Entzerrern betrachtet. Insgesamt soll dabei eine große SI/PI Datenbank entstehen, auf dessen Grundlage ein hybrider Entwurfs-Fluss entstehen, der Daten getriebene und Physik basierte Methoden kombiniert. Dabei wird untersucht, für welche Teilbereiche und in welcher Weise jeweilige ML Methoden optimal eingesetzt werden können.

Finanzierung: Freie und Hansestadt Hamburg

Kontakt: Til Hillebrecht, M.Sc

Start Datum: 17.10.2022

Optimierung von elektronischen Entwicklungsprozessen mit maschinellen Lernmethoden

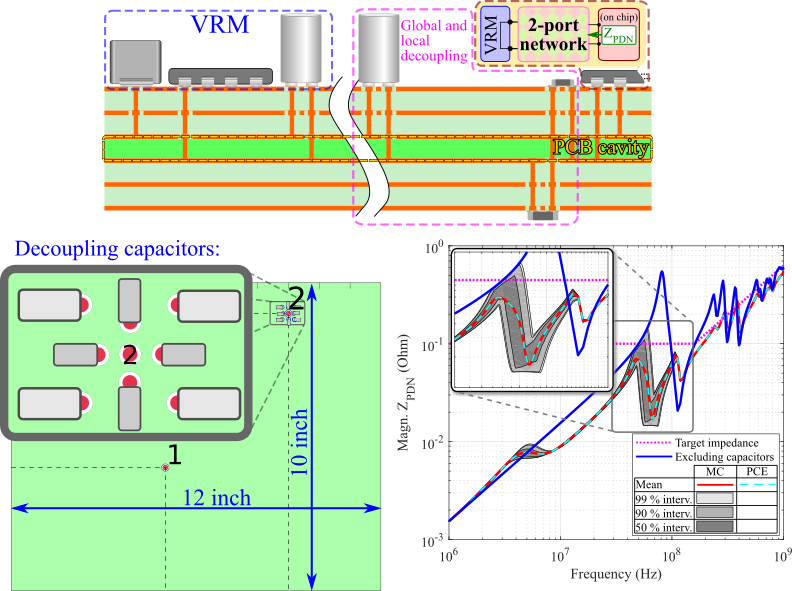

Die Entwicklung modernen mehrlagen Leiterplatten ist eine herausfordernde Aufgabe, die von zahlreichen Anforderung begleitet wird. Um Fehlentwicklungen zu verhindern und alle Spezifkationen zu erfüllen, wird die Entwicklung durch elektromagnetische Simulation begleitet. Auf Grund der hohen Komplexität benötigen diese Simulationen Zeit und Computerresourcen. Unter der Annahme, dass die Simulationen zukünftiger Entwicklungen noch zeitintensiver werden, ist eine wichtige Aufgabe die Optimierung der Simulationsschritte. Werden die Simulationen nicht beschleuningt, ist das Resultat, dass künftige Layouts mehr Zeit und Kosten in der Entwicklung für benötigen. Im schlimmsten Fall kann der zusätzliche Aufwand zu fehlerhaften Entwicklungen führen. In diesem Projekt ist der Fokus auf der Optimierung von Entwicklungsmethoden und Prozessen. Ein vielversprechendes Mittel ist die Verwendung von maschinellen Lernmethoden. In einigen Publikationen der letzten Jahre können Ansätze gefunden werden, wie diese Methoden einzelne Optimierungsprozesse unterstützen (zum Bsp. die Platzierung von Entkoppelkondensatoren mit Hilfe von generischen Algorithmen). Des Weiteren sind mit künstlichen neuronalen Netzen Impedanzen von Leiterplatten untersucht worden und in welcher Form sich die Platzierung von Entkoppelkkondensatoren auf diese auswirkt. Zukünftige Aufgaben sollen die Anwendbarkeit der künstlichen neuronalen Netze zu einem gößeren Spektrum von Simulationsaufgaben erweitern. Der Hauptfokus liegt hierbei auf mehrlagen Leiterplatten, welche die Grundlage der meisten elektronischen Produkte bildet. Eine der wichtigsten Aufgaben in diesem Projekt ist neben der Optimierung von Entwicklungsprozessn die Sicherstellung der Kontinuität von Simulationsergebnisses mit bereits existierenden Methoden.

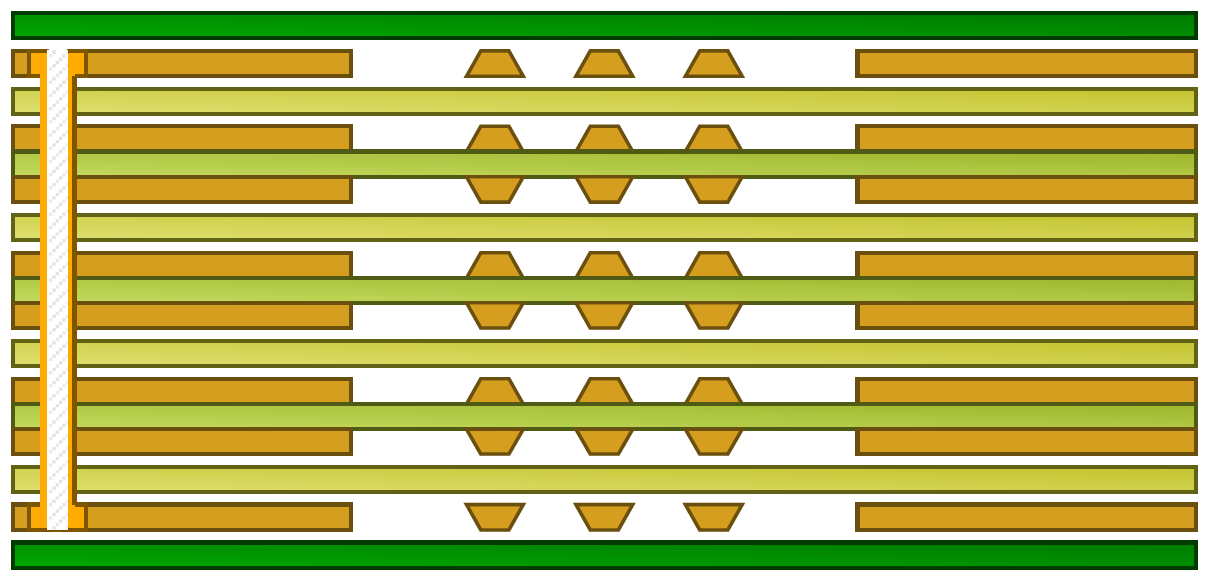

Typische mehrlagige Leiterplatte mit Lagen für die Spannungsversorgung (GND/PWR), sowie zwei Signallagen. Durch Kapazitäten in der Nähe von integrierten Schaltkreisen wird eine Verbesserung der Netzwerkimpedanz angestrebt. Verschiedene Parameter (Materialeigenschaften und Dimensionen) beeinflussen elektronischen Eigenschaften der Leiterplatte.

Die Impedanz der Leiterplattenstruktur verletzt die Zielimpedanz, somit ist dieses Design unzureichend. Die Impedanz der Leiterplattenstruktur kann mit Hilfe von konventionellen Methoden berechnet werden. Die vielversprechende, weniger zeitintensive Methode basiert auf künstlichen neuronalen Netzen. Abhängig von verschiedenen Eingabeparametern (Materialeigenschaften und Dimensionen) werden Vorhersagen über elektronische Eigenschaften getroff en.

Finanzierung: Freie und Hansestadt Hamburg

Kontakt: Morten Schierholz, M.Sc

Start Datum: 01.10.2021

Anwendung von Model Order Reduction Techniken auf die Simulation komplexer elektrischer Verbindungen

Die elektrischer Verbindungen in modernen elektronischen Systemen stellen sehr dichte und komplexe Strukturen dar, die hocheffiziente Methoden für ihre Modellierung und ihr Design erfordern. Auch bei semi-analytischen oder hybriden Simulationsansätzen bedeutet die Analyse dieser Art von Systemen oft sehr große Modelle und lange Rechenzeiten. Dieses Projekt, das in Zusammenarbeit mit dem Instituto Tecnológico de Costa Rica (ITCR) entwickelt wurde, beschäftigt sich mit der Erforschung numerischer Techniken, um die Handhabung, Verkettung und Verarbeitung solcher komplexen Modelle zu erleichtern.

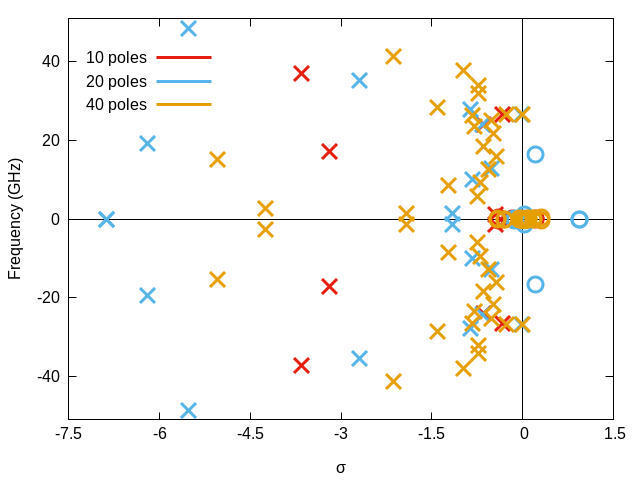

Verschiedene Makromodelltechniken, wie z. B. Vector Fitting und Matrixzustandsdarstellungen, werden als zusätzliche Ressource erforscht, die die Handhabung, Verkettung und Verarbeitung von elektrischen Verbindungen unterstützen kann. Stochastische Makromodelle im Frequenzbereich, die die Deskriptor-Zustandsraum Beschreibung für ein dynamisches System mit Polynomial Chaos Expansion kombinieren, werden ebenfalls analysiert. Dies ermöglicht es, die Variabilitätsanalyse des Systems für jede Frequenz über einen gewünschten Frequenzbereich einzuschließen. Um die Anzahl der benötigten Abtastungen zu reduzieren, werden Techniken für die analytische Verkettung von Makromodellen in Deskriptor-Zustandsraum Beschreibung angepasst. Zusammen mit dem Einsatz von semi-analytischen Techniken für die Wahl der Abtastung sollte dieser Prozess die genaue Darstellung komplexer Multiport-Systeme mit unterschiedlichen zufälligen Eingangsgrößen innerhalb kurzer Zeit ermöglichen. Um die Leistungsfähigkeit dieser Techniken zu bewerten, werden sie mit rein numerischen Techniken mit realistischen Modellierungsszenarien verglichen werden.

Finanzierung: Instituto Tecnologico de Costa Rica (ITCR)

Kontakt: Luis Ernesto Carrera Retana, M. Sc., Prof. Renato Rimolo-Donadio

Start: 01.01.2017

Relevante Publikationen:

Construction of Reciprocal Macromodels in the Loewner Matrix Framework Artikel In: IEEE Transactions on Microwave Theory and Techniques, vol. 71, no. 8, pp. 3561-3571, 2023. |

Improving Accuracy After Stability Enforcement in the Loewner Matrix Framework Artikel In: IEEE Transaction on Microwave Theory and Techniques, vol. 70, no. 2, pp.1037-1047, 2022. |

Efficient Construction of Interconnect Passive Macromodels Through Segmented Analysis Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, Oct. 14-17, 2018. |

Evaluation of Concatenation Techniques for State-Space Interconnect Macromodels”, IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS) Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, Oct. 15-18, 2017. |

Evaluation of Vector Fitting for Compact Interconnect Model Representation Proceedings Article In: IEEE Convention of Central America and Panama Region (CONCAPAN) San Jose, Costa Rica, 2016. |

Bewertung von Interconnects bis zu 100 GHz mit Hilfe von Maschinellem Lernen

Promotion Katharina Scharff: 16.04.2016 – 15.10.2020

Diese Arbeit präsentiert einen Beitrag zur Bewertung und Modellierung von elektrischen Verbindungen auf Leiterplatten bis 100 GHz unter der Anwendung maschinellen Lernens. Parameterstudien mit verschiedenen Modellen werden mit effizienten numerischen Methoden durchgeführt. Das Übersprechen wird für verschiedene Modelle analysiert. Maschinelles Lernen wird als alternative Entwicklungsmethode eingeführt. Es wird hinsichtlich der Zuverlässigkeit ihrer Vorhersagen und des nötigen Aufwandes untersucht.

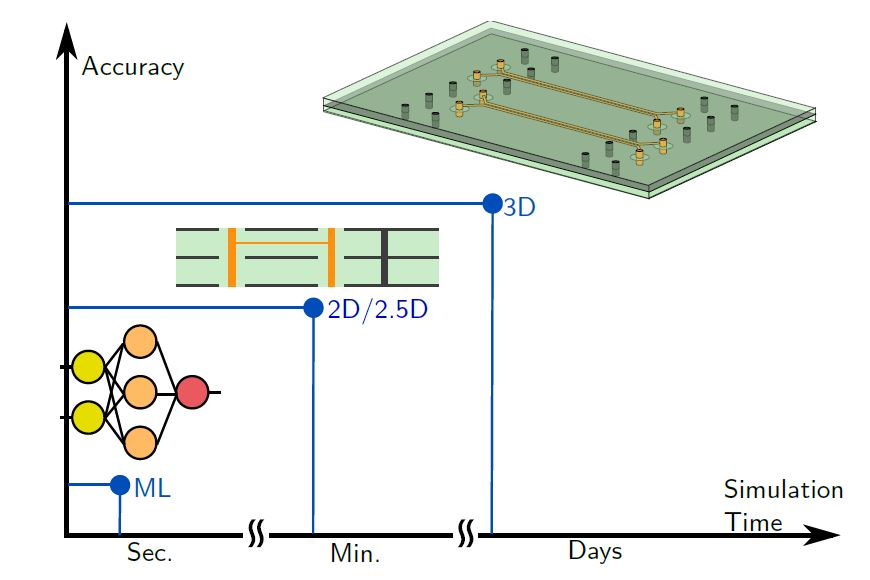

Tools auf Basis von Maschinellem Lernen (ML) zeigen oft sehr kurze Simulationsdauern im Vergleich zu physikbasierten Tools für Anwendungen in der Signalintegrität – seien diese 2D/2.5D oder voll 3D. Allerdings fallen sie in Bezug auf Genauigkeit und Flexibilität zurück. Es kommt deshalb auf einen smarten Einsatz von ML an. (Quelle: TET, TUHH).

Relevante Publikationen:

Bayesian Optimization of First-Order Continuous-Time Linear Equalization in High-Speed Links Including Crosstalk Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Aveiro, Portugal, May 07-10, 2023. |

Evaluation of Interconnects up to 100 GHz Using Machine Learning Promotionsarbeit 2022, ISBN: 978-3-8440-8534-1. |

ANN Performance for the Prediction of High-Speed Digital Interconnects over Multiple PCBs Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS) San Jose, CA, USA, 2020. |

Bayesian Optimization for Signal Transmission Including Crosstalk in a Via Array Proceedings Article In: International Symposium on Electromagnetic Compatibility, Rome, Italy, Sept. 23-25, 2020. |

Evaluation of Neural Networks to Predict Target Impedance Violations of Power Delivery Networks Proceedings Article In: IEEE Conference on Electrical Perfomance of Electronic Packaging and Systems (EPEPS) Montreal, Canada, October 6-9, 2019. |

Mode Conversion Due To Residual Via Stubs in Differential Signaling Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI) Chambery, France, June 18-21, 2019. |

Via Transition Optimization Using a Domain Decomposition Approach Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Chambery, France, June 18-21 2019. |

Performance Metrics for Crosstalk on Printed Circuit Boards in Frequency Domain Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Chambéry, France, June 18-21 2019. |

Efficient Crosstalk Analysis of Differential Links on Printed Circuit Boards Up to 100 GHz Artikel In: IEEE Transactions on Electromagnetic Compatibility, vol. 61, no. 6, pp. 1849-1859, February 26, 2019. |

Physical Scaling Effects of Differential Crosstalk in Via Arrays up to Frequencies of 100 GHz Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Brest, France, May 22 -25, 2018. |

Efficient Prediction of Equalization Effort and Channel Performance for PCB-Based Data Links Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 7, Nr. 11, 2017. |

Exploration of Differential Via Stub Effect Mitigation by Using PAM4 and PAM8 Line Coding Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Lake Maggiore (Baveno), Italy, May 7-10, 2017. |

Exploring Efficient Variability-Aware Analysis Method for High-Speed Digital Link Design Using PCE Proceedings Article In: UBM DesignCon Conference, Santa Clara, CA, USA, January 31 – February 2, 2017. |

Variability Analysis of via Crosstalk using Polynomial Chaos Expansion Proceedings Article In: UBM DesignCon Conference, Santa Clara, CA, USA, January 31-February 2, 2017. |

Impact of Continuous Time Linear Equalizer Variability on Eye Opening of High-Speed Links Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Turin, Italy, May 8-11, 2016. |

Stochastische Randintegralmethodik für die Berechnung zweidimensionaler elektromagnetischer Wellenausbreitung

David Dahl, DFG-Projekt 01.08.2015 – 31.07.2018

Das Projekt soll die so genannte Randintegralmethode zur Berechnung zweidimensionaler elektrotechnischer Aufbau- und Verbindungsstrukturen wie z.B. Leiterplatten und planaren optischen Substraten unter Einbeziehung stochastischer Randbedingungen und Simulations-Parameter mathematisch analysieren, numerisch effizient umsetzen und an ingenieurwissenschaftlich relevanten Beispielen demonstrieren. Zur Berücksichtigung stochastischer Bedingungen und Parameter soll die aus anderen Bereichen bekannte Polynomial Chaos Expansion (PCE) verwendet und hier zum ersten Mal auf eine Randintegralmethode für die Elektrodynamik angewendet werden. Dazu soll ein teilweise schon vorhandener Programmcode auf Fortran-Basis um Methoden erweitert werden, die statistische Variationen in der Anregung, dem geometrischen Aufbau und den Materialeigenschaften berücksichtigen können. Im Detail geht es einerseits um die mathematische Analyse der stochastischen Randintegralmethodik, die Demonstration des Verfahrens an geeigneten Beispielen und die Eingrenzung der numerischen Möglichkeiten. Andererseits geht es um die Erweiterung der Methode und des existierenden Programmcodes für stochastische Problemstellungen aus der Hochfrequenztechnik und der planaren integrierten Optik. Eine Demonstration des Potentials der Methodik soll durch Anwendung des entwickelten Codes auf ingenieurwissenschaftlich interessante Strukturen aus der digitalen Datenübertragungstechnik, der Hochfrequenztechnik und der planaren integrierten Optik erfolgen. Durch die Zusammenarbeit des Institutes für Theoretische Elektrotechnik und des Institutes für Mathematik der Technischen Universität Hamburg-Harburg (TUHH) in diesem Projekt wird hierbei mathematisch/numerische Grundlagenforschung in einem ingenieurwissenschaftlich relevanten und anspruchsvollen Anwendungsfeld ermöglicht.

In der planaren Optik kann die Randintegralmethode zur effizienten Berechnung von photonischen Kristallen verwendet werden, mit welchen beispielsweise optische Wellenleiter hergestellt werden können. (Quelle: TET, TUHH).

Relevante Publikationen:

In: IEEE Journal on Multiscale and Multiphysics Computational Techniques, vol. 4, pp. 180-189, 2019. |

Prediction of Frequency Dependent Shielding Behavior for Ground Via Fences in Printed Circuit Boards Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Chambery, France, June 18-21, 2019. |

Quantifying the Impact of RF Probing Variability on TRL Calibration for LTCC Substrates Proceedings Article In: IEEE Electronic Components and Technology Conference (ECTC), Las Vegas, USA, May 28-31 2019. |

Multiscale Simulation of 2D Photonic Crystal Structures Using a Contour Integral Method Artikel In: IEEE Journal on Multiscale and Multiphysics Computational Techniques, vol. 4, pp. 88-97, 2019. |

An Intrusive PCE Extension of the Contour Integral Method and its Application in Electrical Engineering Proceedings Article In: Annual Meeting of the Gesellschaft für Angewandte Mathematik und Mechanik (GAMM), Vienna, Austria, February, 2019. |

Novel method for error estimation in applications of polynomial chaos expansion to stochastic modeling of multi-resonant systems Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, Oct. 14-17, 2018. |

Error Estimation in Applications of Polynomial Chaos Expansion to Stochastic Modeling of multi-Resonant Systems Proceedings Article In: IEEE Conference on Electrical Perfomance of Electronic Packaging and Systems (EPEPS), San Jose, USA, Oct. 14-17, 2018. |

Electromagnetic Modeling and Optimization of Through Silicon Vias Promotionsarbeit 2018, ISBN: 978-3-8440-6009-6. |

Physical Scaling Effects of Differential Crosstalk in Via Arrays up to Frequencies of 100 GHz Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Brest, France, May 22 -25, 2018. |

Feasibility of Uncertainty Quantification for Power Distribution Network Modeling Using PCE and a Contour Integral Method Proceedings Article In: 2018 Joint IEEE International Symposium on Electromagnetic Compatibility & Asia-Pacific Symposium on Electromagnetic Compatibility, Singapore, May 14-17, 2018. |

Effect of 3D Stack-Up Integration on Through Silicon Via Characteristics Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Lake Maggiore (Baveno), Italy, May 7-10, 2017. |

Efficient Total Crosstalk Analysis of Large Via Arrays in Silicon Interposers Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 6, Nr. 12, 2016. |

Modeling of Differential Striplines in Segmented Simulation of Printed Circuit Board Link Proceedings Article In: IEEE Signal and Power Integrity Conference (SIPI 2016), Ottawa, ON, Canada, July 25-29, 2016. |

High Frequency Characterization of Silicon Substrate and through Silicon Vias Proceedings Article In: Electronic Components and Technology Conference (ECTC), Las Vegas, US, May 31 – June 3, 2016. |

On the Upper Bound of Total Uncorrelated Crosstalk in Large Through Silicon Via Arrays Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI) Turin, Italy, May 8-11, 2016. |

A Rigorous Approach for the Rigorous Approach Using Multipole Expansions Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 6, Nr. 1, 2016. |

Efficient Computation of Localized Fields for Through Silicon Via Modeling Up to 500 GHz Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 5, Nr. 12, 2015. |

Comparison of Passivation Materials for High frequency 3D Packaging Application up to 110 GHz Proceedings Article In: 2015 European Microelectronics Packaging Conference (EMPC), Friedrichshafen, Germany, September 14-16, 2015. |

Efficient Calculation of External Fringing Capacitances for Physics-Based PCB Modeling Workshop 2015 IEEE 19th Workshop on Signal and Power Integrity (SPI), Berlin, Germany, May 10-13, 2015. |

2015 IEEE 19th Workshop on Signal and Power Integrity (SPI), Berlin, Germany, May 10-13, 2015. |

Effect of Layered Media on the Parallel Plate Impedance of Printed Circuit Boards Proceedings Article In: EEE Electrical Design of Advanced Packaging and Systems (EDAPS) Symposium, Bangalore, India, December 14-16, 2014. |

Analysis of Wave Propagation along Coaxial Through Silicon Vias Using a Matrix Method Workshop IEEE Workshop on Signal and Power Integrity (SPI), Ghent, Belgium, May 11-14, 2014. |

Applying a physics-based via model for the simulation of Through Silicon Vias Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, USA, October 27-30, 2013. |

IEEE Workshop on Signal and Power Integrity (SPI), Paris, France, May-12-15, 2013. |

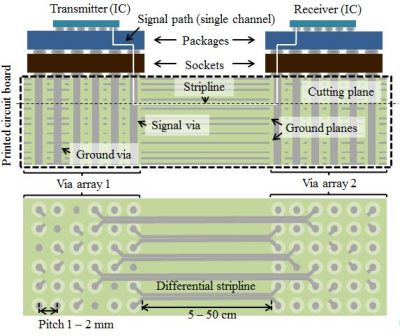

Kombinierte Bewertung von Interconnect und Entzerrung für Datenverbindungen auf mehrlagigen Leiterplatten

Promotion Torsten Reuschel. 01.10.2013 – 15.10.2018

Steigende Datenraten und schwindende Toleranzgrenzen stehen im direkten Gegensatz zum Detailreichtum digitaler Hochgeschwindigkeitsdatenverbindungen, welche sich unter

anderem aus dem passiven Kanal, Entzerrern sowie der Signalkodierung in Form von physikalischen Symbolen zusammensetzen. Dieses Werk stellt neue, recheneffiziente Methoden für den Entwurf und die Prüfung von Datenverbindungen vor. Hierfür wird eine Systemperspektive eingeführt, welche vorherrschende physikalische Parameter des Kanals mit Kennwerten der eingesetzten Entzerrer vereint. Diese Sichtweise erlaubt eine

systematische Auslotung von Randbedingungen und wird durch eine Studie über fortgeschrittenen Methoden der Quantifizierung von Parameterunsicherheiten im Entwurf von Datenverbindungen ergänzt.

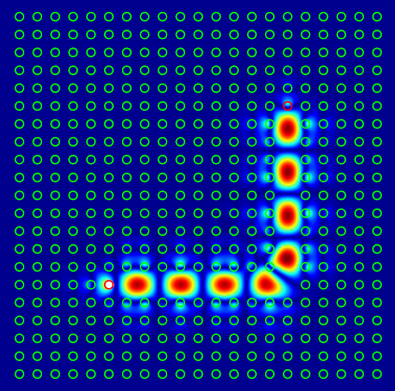

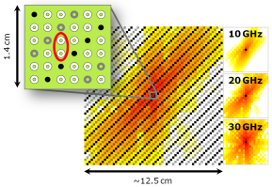

Verteilung des Übersprechens (Crosstalk) in einem großen Via-Array bei unterschiedlichen Frequenzen. Berechnet mit dem institutseigenen Werkzeug Multilayer Substrate Simulator. (Quelle: TET, TUHH). (Quelle: TET, TUHH).

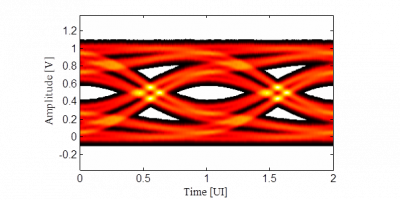

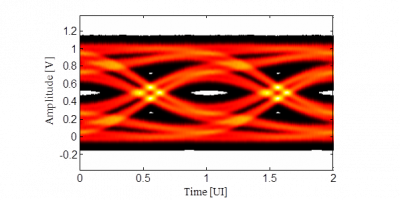

Exemplarischer Interconnect zwischen zwei großen Via-Arrays; gezeigt ist nur die Anordnung der Streifenleitungen in der obersten Kavität. Das Augendiagramm wird mittels statistischen Methoden zeiteffizient ermittelt. (Quelle: TET, TUHH).

Relevante Publikationen:

Automated Generation and Correlation of Physics-Based Via Models with Full-Wave Simulation for an SI/PI Database Proceedings Article In: Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), Milpitas, CA, USA, October 15-18, 2023. |

Modeling Electrically Long Interconnects Using Physics-Informed Delayed Gaussian Processes Artikel In: IEEE Transactions on Electromagnetic Compatibility, vol. 65, no. 6, pp. 1715 - 1723, 2023. |

Modeling S-parameters of Interconnects using Periodic Gaussian Process Kernels Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Aveiro, Portugal, May 07-10, 2023. |

Combined Assessment of Interconnect and Equalization in Data Links on Multilayer Printed Circuit Boards Promotionsarbeit 2019, ISBN: 978-3-8440-6499-5. |

Direct Prediction of Linear Equalization Coefficients Using Raised Cosine Pulse Shaping in Frequency Domain Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Brest, France, May 22-25, 2018. |

Efficient Sensitivity-Aware Assessment of High-Speed Links Using PCE and Implications for COM Proceedings Article In: DesignCon, Santa Clara, CA, USA, January, 2018. |

Efficient Prediction of Equalization Effort and Channel Performance for PCB-Based Data Links Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 7, Nr. 11, 2017. |

Efficient Design of Continuous Time Linear Equalization for Loss Dominated Digital Links Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Lake Maggiore (Baveno), Italy, May 7-10, 2017. |

Exploration of Differential Via Stub Effect Mitigation by Using PAM4 and PAM8 Line Coding Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Lake Maggiore (Baveno), Italy, May 7-10, 2017. |

An Electronically Scannable Reflector Antenna Using a Planar Active Array Feed at Ka-Band Artikel In: IEEE Transactions on Microwave Theory and Techniques, Bd. 65, Nr. 5, 2017. |

Redundant and Non-Redundant Spectrum Shaping Schemes for Reflection-Limited Chip-to-Chip Communication Proceedings Article In: International ITG Conference on Systems, Communication and Coding (SCC) Hamburg, Germany, February 6-9, 2017. |

Variability Analysis of via Crosstalk using Polynomial Chaos Expansion Proceedings Article In: UBM DesignCon Conference, Santa Clara, CA, USA, January 31-February 2, 2017. |

Exploring Efficient Variability-Aware Analysis Method for High-Speed Digital Link Design Using PCE Proceedings Article In: UBM DesignCon Conference, Santa Clara, CA, USA, January 31 – February 2, 2017. |

Efficient Total Crosstalk Analysis of Large Via Arrays in Silicon Interposers Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 6, Nr. 12, 2016. |

Ansatz zur Verbesserung des Vorstellungsvermögens elektromagnetischer Felder der Studierenden im Modul „Theoretische Elektrotechnik I: Zeitunabhängige Felder“ Artikel In: Praxisprojekte des Qualifizierungsprogramms „Forschendes Lernen an der TUHH“, Ausgabe 2. Hamburg, Germany: Zentrum für Lehre und Lernen, Technische Universität Hamburg, 2016. |

On the Treatment of Arbitrary Boundary Conditions Using a Fast Direct H-Matrix Solver in MoM Artikel In: IEEE Transactions on Antennas and Propagation, Bd. 64, Nr. 8, 2016. |

Modeling of Differential Striplines in Segmented Simulation of Printed Circuit Board Link Proceedings Article In: IEEE Signal and Power Integrity Conference (SIPI 2016), Ottawa, ON, Canada, July 25-29, 2016. |

On the Upper Bound of Total Uncorrelated Crosstalk in Large Through Silicon Via Arrays Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI) Turin, Italy, May 8-11, 2016. |

Impact of Continuous Time Linear Equalizer Variability on Eye Opening of High-Speed Links Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Turin, Italy, May 8-11, 2016. |

Segmented Physics-Based Modeling of Multilayer Printed Circuit Boards Using Stripline Port Artikel In: IEEE Transactions on Electromagnetic Compatibility, Bd. 58, Nr. 1, 2016. |

Systematic analysis of electrical link bottlenecks and strategies for their equalization Proceedings Article In: DesignCon, Santa Clara, CA, USA, 19. -21. January , 2016. |

Energy-Aware Signal Integrity Analysis for High-Speed PCB Links Artikel In: IEEE Transactions on Electromagnetic Compatibility, Bd. 57, Nr. 5, 2015. |

Investigation of Long Range Differential Crosstalk on Printed Circuit Boards Workshop EEE Workshop on Signal and Power Integrity (SPI), Ghent, Belgium, May 11-14, 2014. |

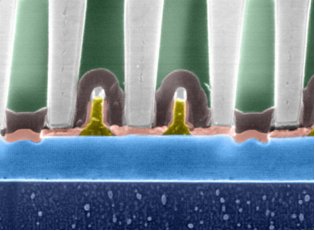

Elektromagnetische Modellbildung und Optimierung von Silizium-Durchkontaktierungen

Promotion David Dahl. 01.10.2012 – 13.12.2017

Die vorliegende Arbeit beschreibt die Simulation und den Entwurf von Durchkontaktierungen in Siliziumsubstraten (TSVs), wie sie in der Aufbau- und Verbindungstechnik für integrierte Schaltkreise Anwendung finden. Numerische Verfahren von vergleichsweise hoher numerischer Effizienz werden entwickelt und angewendet, um realistische Anordnungen mit großen Anzahlen von TSVs simulieren zu können. Die vorgestellten Methoden werden mit alternativen Ansätzen korreliert und aus Parametervariationen werden Designempfehlungen abgeleitet. Des Weiteren werden mehrere Messstrukturen mit TSVs entwickelt und Messergebnisse für diese mit Simulationsergebnissen vergleichen.

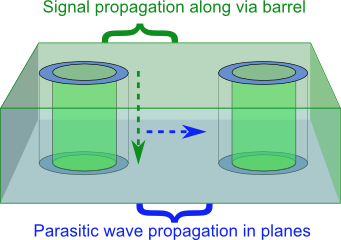

Schematischer Aufbau eines Teils eines Silizium-Interposers, in welchem TSVs eine Verbindung zwischen Ober- und Unterseite herstellen. Die metallischen Zylinder von typischerweise kreisförmigem Querschnitt sind vom leitfähigen Siliziumsubstrat durch eine Siliziumdioxidschicht elektrisch isoliert. Wie im Bild angedeutet, werden zwei hauptsächliche Arten der Propagation in dieser Struktur untersucht. (Quelle: TET, TUHH).

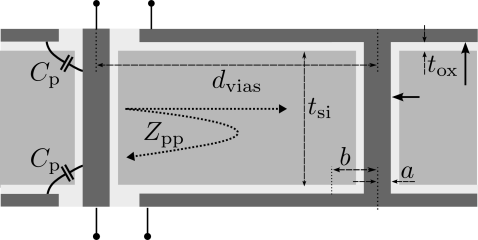

Das physikbasierte Via-Modell nimmt metallische Berandungen zu beiden Seiten der Interposer-Struktur an. Nahfeldeffekte werden von konzentrierten Elementen (hier Kapazitäten) dargestellt, während die Ausbreitung in der Kavität aus Substrat und den Metallisierungen durch die Parallel-Platten-Impedanz dargestellt wird. (Quelle: TET, TUHH).

Relevante Publikationen:

In: IEEE Journal on Multiscale and Multiphysics Computational Techniques, vol. 4, pp. 180-189, 2019. |

Prediction of Frequency Dependent Shielding Behavior for Ground Via Fences in Printed Circuit Boards Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Chambery, France, June 18-21, 2019. |

Quantifying the Impact of RF Probing Variability on TRL Calibration for LTCC Substrates Proceedings Article In: IEEE Electronic Components and Technology Conference (ECTC), Las Vegas, USA, May 28-31 2019. |

Multiscale Simulation of 2D Photonic Crystal Structures Using a Contour Integral Method Artikel In: IEEE Journal on Multiscale and Multiphysics Computational Techniques, vol. 4, pp. 88-97, 2019. |

An Intrusive PCE Extension of the Contour Integral Method and its Application in Electrical Engineering Proceedings Article In: Annual Meeting of the Gesellschaft für Angewandte Mathematik und Mechanik (GAMM), Vienna, Austria, February, 2019. |

Novel method for error estimation in applications of polynomial chaos expansion to stochastic modeling of multi-resonant systems Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, Oct. 14-17, 2018. |

Error Estimation in Applications of Polynomial Chaos Expansion to Stochastic Modeling of multi-Resonant Systems Proceedings Article In: IEEE Conference on Electrical Perfomance of Electronic Packaging and Systems (EPEPS), San Jose, USA, Oct. 14-17, 2018. |

Electromagnetic Modeling and Optimization of Through Silicon Vias Promotionsarbeit 2018, ISBN: 978-3-8440-6009-6. |

Physical Scaling Effects of Differential Crosstalk in Via Arrays up to Frequencies of 100 GHz Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Brest, France, May 22 -25, 2018. |

Feasibility of Uncertainty Quantification for Power Distribution Network Modeling Using PCE and a Contour Integral Method Proceedings Article In: 2018 Joint IEEE International Symposium on Electromagnetic Compatibility & Asia-Pacific Symposium on Electromagnetic Compatibility, Singapore, May 14-17, 2018. |

Effect of 3D Stack-Up Integration on Through Silicon Via Characteristics Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI), Lake Maggiore (Baveno), Italy, May 7-10, 2017. |

Efficient Total Crosstalk Analysis of Large Via Arrays in Silicon Interposers Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 6, Nr. 12, 2016. |

Modeling of Differential Striplines in Segmented Simulation of Printed Circuit Board Link Proceedings Article In: IEEE Signal and Power Integrity Conference (SIPI 2016), Ottawa, ON, Canada, July 25-29, 2016. |

High Frequency Characterization of Silicon Substrate and through Silicon Vias Proceedings Article In: Electronic Components and Technology Conference (ECTC), Las Vegas, US, May 31 – June 3, 2016. |

On the Upper Bound of Total Uncorrelated Crosstalk in Large Through Silicon Via Arrays Proceedings Article In: IEEE Workshop on Signal and Power Integrity (SPI) Turin, Italy, May 8-11, 2016. |

A Rigorous Approach for the Rigorous Approach Using Multipole Expansions Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 6, Nr. 1, 2016. |

Efficient Computation of Localized Fields for Through Silicon Via Modeling Up to 500 GHz Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 5, Nr. 12, 2015. |

Comparison of Passivation Materials for High frequency 3D Packaging Application up to 110 GHz Proceedings Article In: 2015 European Microelectronics Packaging Conference (EMPC), Friedrichshafen, Germany, September 14-16, 2015. |

Efficient Calculation of External Fringing Capacitances for Physics-Based PCB Modeling Workshop 2015 IEEE 19th Workshop on Signal and Power Integrity (SPI), Berlin, Germany, May 10-13, 2015. |

2015 IEEE 19th Workshop on Signal and Power Integrity (SPI), Berlin, Germany, May 10-13, 2015. |

Effect of Layered Media on the Parallel Plate Impedance of Printed Circuit Boards Proceedings Article In: EEE Electrical Design of Advanced Packaging and Systems (EDAPS) Symposium, Bangalore, India, December 14-16, 2014. |

Analysis of Wave Propagation along Coaxial Through Silicon Vias Using a Matrix Method Workshop IEEE Workshop on Signal and Power Integrity (SPI), Ghent, Belgium, May 11-14, 2014. |

Applying a physics-based via model for the simulation of Through Silicon Vias Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, USA, October 27-30, 2013. |

IEEE Workshop on Signal and Power Integrity (SPI), Paris, France, May-12-15, 2013. |

Software-Benchmarking in der Signal- und Power-Integrität

Industrieprojekt. 01.03.2012 – 31.12.2014

Das Institut für Theoretische Elektrotechnik evaluierte die SEMCAD-Software der SPEAG, ein Feldlöser auf Basis eines FDTD-Algorithmus, in Hinblick auf typische Probleme der Signal- und Power-Integrität beim Entwurf von digitalen Systemen. Die Schmid & Partner Engineering AG (SPEAG) ist ein Zürcher Unternehmen, welches moderne Simulations-Tools und Messgeräte für elektromagnetische Messung in Nah- und Fernfeld und Anwendung vom statischen bis in den optischen Frequenzbereich entwickelt und herstellt. Die SPEAG konzentriert sich dabei auf Auswertung und Optimierung von elektromagnetischen Feldern in komplexen Umgebungen, wie zum Beispiel nahe oder im menschlichen Körper. Der typische Anwendungsbereich umfasst elektromagnetische Sicherheit und Design-Optimierungen von Mobiltelefonen, Magnetresonanztomographie sowie von medizinischen Implantaten.

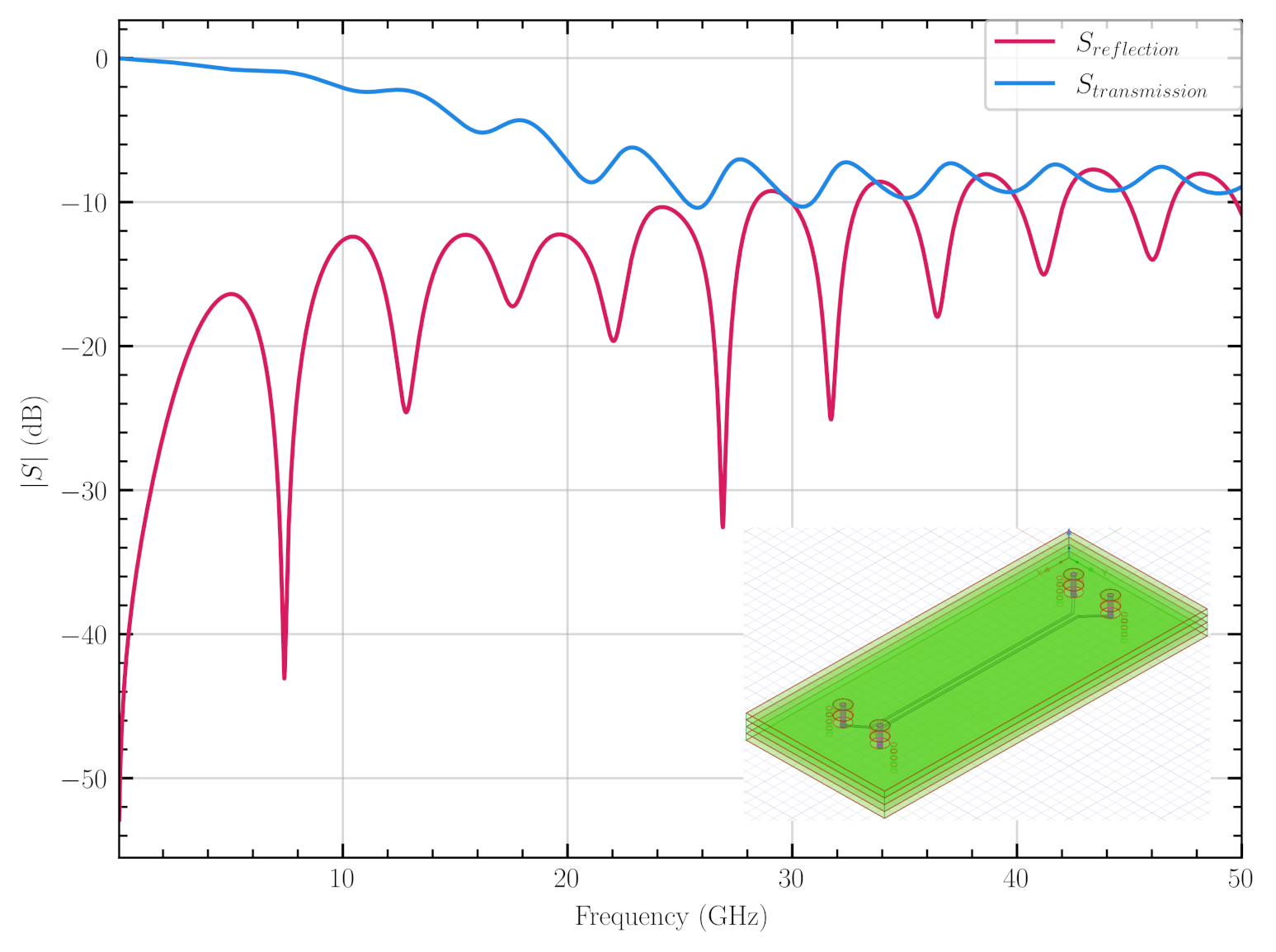

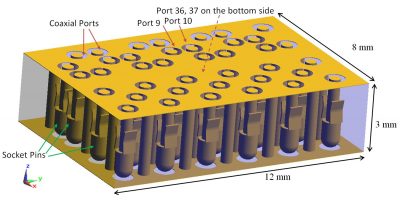

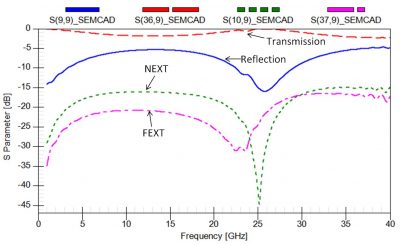

In der Abbildung unterhalb wird ein Benchmark für ein elektrisches Package gezeigt. Ein Modell einer Ball Grid Array (BGA)-Fassung (socket) besteht aus etwa 28 Millionen Gitterzellen. Reflektion, Transmission sowie die Parameter des Übersprechens wurden im Frequenzbereich bis 40 GHz aus Zeitbereichsdaten extrahiert. Es kann beobachtet werden, dass das Übersprechen sein Maximum in einem Frequenzbereich zwischen 10 und 15 GHz erreicht.

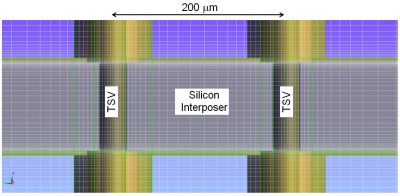

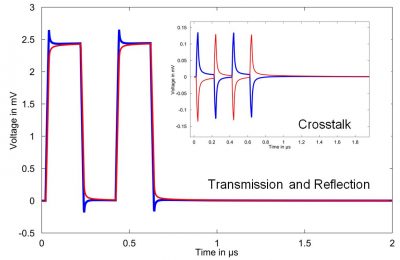

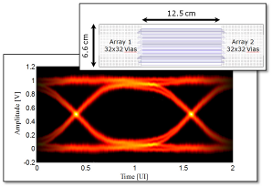

Eine zweiter Benchmark wurde mit dem unten im Detail gezeigten Silizium-Interposer durchgeführt, welcher zwei Silizium-Durchkontaktierungen (through silicon vias, TSVs) aufweist und dessen Modell aus etwa einer Million Gitterzellen besteht. Ergebnisse im Zeitbereich bei Anregung mit zwei digitalen Pulsen werden in der folgenden Abbildung gezeigt. Es kann beobachtet werden, dass die TSVs im Wesentlichen induktive Reflektion zeigen und Übersprechen während der Anstiegs- und Abfallszeiten des Anregungssignals verursacht wird.

Entwurf von 50+ Gbps High Speed Serial Links für digitale Systeme

Industrieprojekt. 01.08.2014 – 31.10.2014

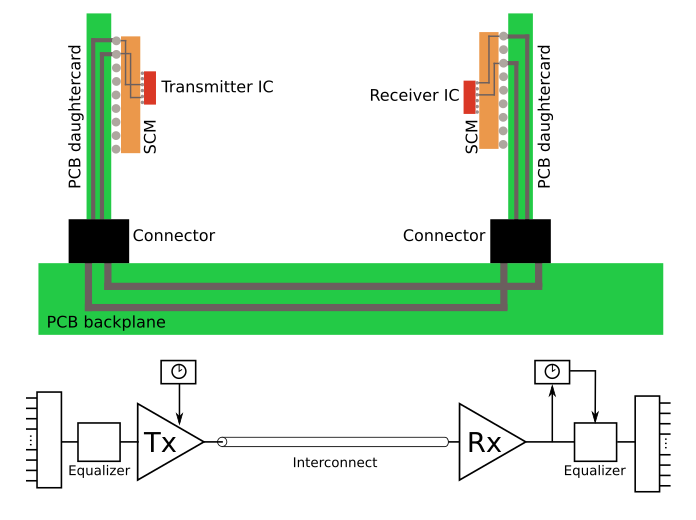

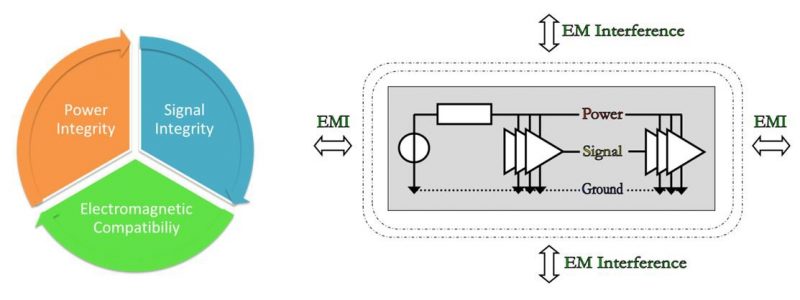

Der Entwurf von High Speed Serial Link für digitale Systeme nähert sich in seinen Datenraten schnell dem Bereich 25-50 Gbps und wird diesen in der nächsten Dekade wohl noch überschreiten. Diesen Trend kann man u.a. festmachen an der kürzlich gestarteten 56 Gbps Common Electrical Interface (CEI) Initiative des Optical Internetworking Forum (OIF). Mit dem Anstieg der Datenrate werden Probleme in den Feldern der Signal-Integrität (SI), der Power-Integrität (PI) und der elektromagnetischen Verträglichkeit (EMV) weiter ansteigen und dementsprechend Aufmerksamkeit verlangen, wenn Systeme nicht in ihrer elektrischen Integrität gefährdet werden sollen (siehe Abbildung unten).

In diesem Forschungsprojekt in Zusammenarbeit mit der HUAWEI Forschung Europa hat das Institut für Theoretische Elektrotechnik den Stand der Technik, die technischen Herausforderungen und die notwendigen Schritte für die elektrische Integrität bei solchen Datenraten recherchiert und untersucht. Dabei wurden insbesondere folgende Aspekte betrachtet:

– wesentliche Elemente erfolgreicher Entwurfsstrategien für Links,

– notwendige CAD-Werkzeuge für den Entwurf von Links,

– besondere Probleme und Herausforderungen bei 50+ Gbps Übertragung,

– passende Aufbau- und Verbindungstechnik für 50+ Gbps Übertragung,

– wichtigste Forschungsthemen der nächsten Zukunft.

Die Ergebnisse wurden in einem White Paper zusammengefasst und bei HUAWEI präsentiert.

Das Konzept der elektrischen Integrität für digitale Systeme: Typischerweise werden drei Aspekte der elektrischen Integrität unterschieden (links): Power-Integrität, Signal-Integrität und elektromagnetische Verträglichkeit. Obwohl alle drei über verschiedene Zielstellungen und Methoden verfügen, sind diese Aspekte eng miteinander verknüpft. Die schematische Darstellung (rechts) illustriert die Zielvorstellungen der verschiedenen Aspekte, die verkürzt wie folgt beschrieben werden können: Die Power-integrität stellt eine stabile Spannungsversorgung sicher, die Signal-Integrität stellt die Qualität von transmittierten Signalen sicher und die elektromagnetische Verträglichkeit stellt ein niedriges Niveau elektromagnetischer Interferenzen sicher.

Modellierung von Via-Arrays für die Anwendung in schnellen energieeffizienten digitalen Systemen

Promotion Sebastian Müller. 01.04.2010 – 31.07.2014

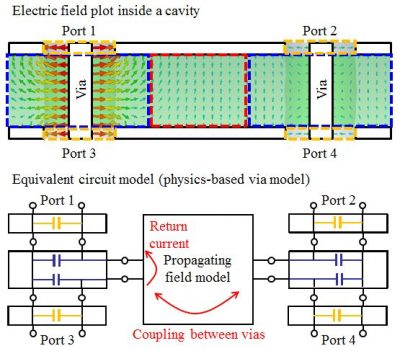

Die vorgelegte Arbeit betrachtet die Anwendung quasianalytischer (sogenannter “physics-based”) Viamodelle zur genauen und effizienten Modellierung von Via-Arrays in mehrlagigen Leiterplatten. Die Arbeit beinhaltet drei Hauptaspekte: eine Untersuchung und Verbesserung der Modellgenauigkeit, eine Untersuchung und Verbesserung der Modelleffizienz und eine Anwendung des Modells im Rahmen eines systematischen Vergleichs verschiedener Designalternativen für Verbindungen mit hohen Datenraten auf Leiterplatten. Eine Verbesserung der Modellgenauigkeit wird vor allem durch eine verbesserte Nahfeldmodellierung erreicht, die die Simulationsergebnisse insbesondere für Frequenzen oberhalb von 20 GHz verbessert. Mit dem verbesserten Modell wird die genaue Simulation großer Via-Arrays für Viaabstände bis hinab zu 60 mil im Frequenzbereich bis 50 GHz möglich. Verschiedene Verbesserungen im Hinblick auf die Modelleffizienz führen zu einer Reduzierung der Rechenzeiten, die eine schnelle Untersuchung von Designalternativen für kleinere Via-Arrays auf einem einfachen PC ermöglicht. Am Ende der Arbeit wird eine Vorgehensweise für eine systematische Bewertung von Designalternativen vorgestellt. Die Vorgehensweise erlaubt einen quantitativen Vergleich von Designalternativen, der die Auswirkung von Designänderungen auf Signalintegrität und Energieeffizienz im gesamten System berücksichtigt.

(Quelle: TET, TUHH)

(Quelle: TET, TUHH)

Relevante Publikationen:

Segmented Physics-Based Modeling of Multilayer Printed Circuit Boards Using Stripline Port Artikel In: IEEE Transactions on Electromagnetic Compatibility, Bd. 58, Nr. 1, 2016. |

Energy-Aware Signal Integrity Analysis for High-Speed PCB Links Artikel In: IEEE Transactions on Electromagnetic Compatibility, Bd. 57, Nr. 5, 2015. |

Effect of Layered Media on the Parallel Plate Impedance of Printed Circuit Boards Proceedings Article In: EEE Electrical Design of Advanced Packaging and Systems (EDAPS) Symposium, Bangalore, India, December 14-16, 2014. |

Including multiconductor transmission lines in a quasi-analytical model for multilayer structures Promotionsarbeit 2014, ISBN: 978-3-8440-3360-1. |

High Frequency Measurement Techniques for Vias in Printed Circuit Boards Artikel In: IEEE Electromagnetic Compatibility Magazine, Bd. 3, Nr. 4, 2014. |

Investigation of Long Range Differential Crosstalk on Printed Circuit Boards Workshop EEE Workshop on Signal and Power Integrity (SPI), Ghent, Belgium, May 11-14, 2014. |

Energy-aware analysis of electrically long high speed I/O links Artikel In: Computer Science – Research and Development, Bd. 29, Nr. 2, 2014. |

Einfluss der Routinglage in Via-Arrays auf die Signalqualität bei hohen Datenraten Proceedings Article In: Internationale Fachmesse und Kongress für Elektromagnetische Verträglichkeit (EMV Düsseldorf) , Düsseldorf, Germany, March 11-13, 2014. |

In: IEEE Electromagnetic Compatibility Magazine, Bd. 3, Nr. 1, 2014. |

Analytical Extraction of Via Near-Field Coupling Using a Multiple Scattering Approach Workshop EEE Workshop on Signal and Power Integrity (SPI) Paris, Frankreich, 2013. |

Complete Modeling of Large Via Constellations in Multilayer Printed Circuit Boards Artikel In: IEEE Transactions on Components, Packaging and Manufacturing Technology, Bd. 3, Nr. 3, 2013. |

Signal and Power Integrity (SPI) Co-Analysis for High-Speed Communication Channels Proceedings Article In: UBM DesignCon Conference, Santa Clara, USA, January 28-31, 2013. |

Minimizing Displacement Return Currents in Multilayer Via Structures Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), Tempe, USA, October 21-24, 2012. |

Accuracy of Physics-Based Via Models for Simulation of Dense Via Arrays Artikel In: IEEE Transactions on Electromagnetic Compatibility, Bd. 54, Nr. 5, 2012. |

Energy-Aware Analysis of Electrically Long High Speed I/O Links Artikel In: Computer Science – Research and Development, August 2012 and International Conference on Energy-Aware High Performance Computing (EnA-HPC), Hamburg, Germany, September 12, 2012. |

Efficient, Physics-Based Via Modeling: Integration of Striplines (invited) Artikel In: IEEE Electromagnetic Compatibility Magazine, Bd. 1, Nr. 2, 2012. |

Analytical Calculation of Conduction and Displacement Current Contributions in PCB Return Current Paths Proceedings Article In: Asia-Pacific EMC Symposium (APEMC), Singapore, May 21-24, 2012. |

Anwendung quasianalytischer Via-Modelle zur schnellen Simulation dichter Via-Arrays Proceedings Article In: Internationale Fachmesse und Kongress für Elektromagnetische Verträglichkeit (EMV Düsseldorf), Düsseldorf, Germany, February 7-9, 2012. |

Backplane Channel Design Optimization: Recasting a 3Gb/s Link to Operate at 25Gb/s and Above Proceedings Article In: UBM DesignCon Conference, Santa Clara, CA, USA, January 30-February 2, 2012. |

Impact of Multiple Scattering on Passivity of Equivalent-Circuit Via Models Proceedings Article In: IEEE Electrical Design of Advanced Package & Systems Symposium (EDAPS), Hangzhou, China, December 12-14, 2011. |

Recent Developments of Via and Return Current Path Modeling (Invited) Proceedings Article In: International Conference on Electromagnetics in Advanced Applications (ICEAA), Torino, Italy, September 12-16, 2011. |

Validation and Application of Physics-based Via Models to Dense Via Arrays Proceedings Article In: IEC DesignCon Conference, Santa Clara, USA, January 31-February 3, 2011. |

Non-Uniform Currents on Vias and Their Effects in a Parallel-Plate Environment Proceedings Article In: IEEE Electrical Design of Advanced Package & Systems Symposium (EDAPS), Singapore, December 7-9, 2010. |

Effect of Mixed-Reference Planes on Single-Ended and Differential Links in Multilayer Substrates Workshop IEEE Workshop on Signal Propagation on Interconnects (SPI), Hildesheim, Germany, May 9-12, 2010. |

Schnelle Simulation verlustbehafteter Verbindungsstrukturen auf Leiterplatten auf der Grundlage quasianalytischer Via-Modelle und der Leitungstheorie Proceedings Article In: Internationale Fachmesse und Kongress für Elektromagnetische Verträglichkeit (EMV Düsseldorf), Düsseldorf, Germany, March 9-11, 2010. |

Untersuchung des Einflusses von Schwankungen der Versorgungsspannung auf die maximalen Datenraten von schnellen digitalen Verbindungen in modernen Server-Systemen

Industrie Projekt. 18.06.2010 – 17.06.2013

Schnelle digitale Verbindungen in IBM’s Serever-Systemen zeigen heutzutage Datenraten von 10 Gigabit pro Sekunde (Gbps) und mehr. Diese Verbindungen sind wesentlich für die insgesamte Systemleistung und werden sorgfältig in Bezug auf Signalintegrität und Bit-Fehlerraten entworfen. Der Entwurfsprozess geht dabei iterativ vor, wobei I/O Schaltkreis-Entwickler und Package-Entwickler gemeinsam die Verbindungsleistung unter Verwendung geeigneter Modelle für die Komponenten des Kommunikationssystems optimieren. Mit steigenden Datenraten (mehr als 12 Gbps in der nächsten Generation) werden sich die zugrundeliegenden Stör-Kopplungsmechanismen ändern und eine Nächste-Nachbarn-Analyse weniger aussagkräftig machen. Auch verlassen sich neuere Architekturen in zunehmenden Maße auf differentielle Signalführung, um die Störfestigkeit zu erhöhen. Mit ansteigenden Datenraten werden deshalb neu Kopplungsmechanismen auftauchen, von denen viele Abhängigkeiten von Skew, Schwankungen der Versorgungsspannung und Diskontinuitäten im Rückstrompfad zeigen werden.

IBM Watson Supercomputer auf Basis des Power7 (Bildquelle: IBM)

Transistoren auf einem IBM Power6 Chip (Bildquelle: IBM)

Der heutige Entwurfsprozess für schnellen digitalen Verbindungen konzentriert sich auf die Leistung der Signalleitung. Der Entwurf des Spannungsversorgungssystems ist üblicherweise davon losgelöst und sein Einfluss auf die Signalqualität und die maximal erreichbare Datenrate wird nicht regelmäßig überprüft oder quantitativ erfasst. In diesem gemeinsamen Forschungsprojekt des Institutes für Theoretische Elektrotechnik und einer Abteilung der IBM Deutschland Research & Development GmbH wurdr der Einfluss von Schwankungen der Spannungsversorgung auf die maximalen Datenraten von schnellen digitalen Verbindungen IBMs untersucht. Das Team entwickelte hierbei erfolgreich ein Modell für die Aufbau- und Verbindungstechnik der Spannungsversorgung und eine Methode um so genannten simultaneous switching noise bei Kanalkapazitätsberechnungen zu berücksichtgen.

Simuliertes Augendiagramm einer schnellen

digitalen Verbindungen.

Simuliertes Augendiagramm unter dem Einfluss einer schwankenden Versorgungsspannung.

Relevante Publikationen:

Modeling of Power Supply Noise Effects on High Speed Interconnects Workshop EMC Symposium (APEMC), Melbourne, Australia, Mai 20-23, 2013. |

Signal and Power Integrity (SPI) Co-Analysis for High-Speed Communication Channels Proceedings Article In: UBM DesignCon Conference, Santa Clara, USA, January 28-31, 2013. |

Framework for Co-Simulation of Signal and Power Integrity in Server Systems Proceedings Article In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), Tempe, USA, October 21-24, 2012. |

IEEE Workshop on Signal and Power Integrity (SPI), Sorrento, Italy, May 13-16, 2012. |

Entwicklung, Validation und Anwendung von semianalytischen Interconnect Modellen für die effiziente Simulation von Multilagensubstraten

Promotion Renato Rimolo-Donadio. 01.11.2006 – 31.12.2010

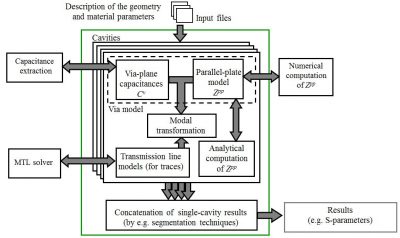

Das Projekt befasst sich mit der Entwicklung von semianalytischen Modellen für das elektrische Verhalten von Durchkontaktierungen und Leitungen in Chip-Modulen und Leiterplatten. Ein Verfahren für die automatisierte Simulation von mehrlagigen Strukturen wird ebenso dargestellt. Die Modelle werden gründlich anhand von mehreren Teststrukturen und Anwendungsstudien validiert und ausgewertet. Es wird gezeigt, dass die Modelle gute Ergebnisse bis 40 GHz liefern und eine numerische Effizienz bieten, die mindestens zwei Größenordnungen höher ist im Vergleich zu allgemeinen numerischen Verfahren.

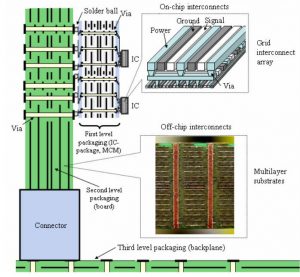

Illustration of interconnect levels in high-speed electronic systems. On-chip interconnects mainly consist of metallization layers of IC technologies, which are typically arranged as grid meshes. Off-chip interconnects cover the first (package and MCM), second (board), and third (motherboard/backplane) levels. Multilayer substrates are used to support the off-chip signal and power networks. (Quelle: TET, TUHH).

Relevante Publikationen:

FNNs Models for Regression of S-Parameters in Multilayer Interconnects with Different Electrical Lengths Proceedings Article In: 2023 IEEE MTT-S Latin America Microwave Conference (LAMC), San José, Costa Rica, December 06-08, 2023. |

Construction of Reciprocal Macromodels in the Loewner Matrix Framework Artikel In: IEEE Transactions on Microwave Theory and Techniques, vol. 71, no. 8, pp. 3561-3571, 2023. |

Impact of Multiple Scattering on Passivity of Equivalent-Circuit Via Models Proceedings Article In: IEEE Electrical Design of Advanced Package & Systems Symposium (EDAPS), Hangzhou, China, December 12-14, 2011. |

Recent Developments of Via and Return Current Path Modeling (Invited) Proceedings Article In: International Conference on Electromagnetics in Advanced Applications (ICEAA), Torino, Italy, September 12-16, 2011. |

A Hybrid CIM/MoM Approach for Power Plane Analysis Including Radiation Loss Proceedings Article In: Asia-Pacific EMC Symposium (APEMC), Jeju Island, Korea, May-16-19, 2011. |

Fast Parametric Pre-Layout Analysis of Signal Integrity for Backplane Interconnects Proceedings Article In: IEEE Workshop on Signal Propagation on Interconnects (SPI), Naples, Italy, May 8-11, 2011. |

Validation and Application of Physics-based Via Models to Dense Via Arrays Proceedings Article In: IEC DesignCon Conference, Santa Clara, USA, January 31-February 3, 2011. |

Development, Validation, and Application of Semi-analytical Interconnect Models for Efficient Simulation of Multilayer Substrates Promotionsarbeit 2011, ISBN: 978-3-8325-2776-1 . |

Non-Uniform Currents on Vias and Their Effects in a Parallel-Plate Environment Proceedings Article In: IEEE Electrical Design of Advanced Package & Systems Symposium (EDAPS), Singapore, December 7-9, 2010. |

Effect of Mixed-Reference Planes on Single-Ended and Differential Links in Multilayer Substrates Workshop IEEE Workshop on Signal Propagation on Interconnects (SPI), Hildesheim, Germany, May 9-12, 2010. |

Multiport Measurement and Deembedding Techniques for Crosstalk Study in Via Arrays Workshop IEEE Workshop on Signal Propagation on Interconnects (SPI), Hildesheim, Germany, May 9-12, 2010. |

In: IEEE Transactions on Electromagnetic Compatibility , Bd. 52, Nr. 2, 2010. |

Fast and Concurrent Simulations for SI, PI, and EMI Analysis of Multilayer Printed Circuit Boards (invited) Proceedings Article In: Asia-Pacific Symposium on EMC (APEMC), Beijing, China, April 12-16, 2010. |

Schnelle Simulation verlustbehafteter Verbindungsstrukturen auf Leiterplatten auf der Grundlage quasianalytischer Via-Modelle und der Leitungstheorie Proceedings Article In: Internationale Fachmesse und Kongress für Elektromagnetische Verträglichkeit (EMV Düsseldorf), Düsseldorf, Germany, March 9-11, 2010. |

Special Session on Power Integrity Techniques: Contour Integral Method for Rapid Computation of Power/Ground Plane Impedance Proceedings Article In: IEC DesignCon Conference, Santa Clara, USA, February 1-4, 2010. |

Fast-Physics-Based Via and Trace Models for Signal and Power Integrity Co-Analysis Proceedings Article In: IEC DesignCon Conference, Santa Clara, USA, February 1-4, 2010. |

Comprehensive Multilayer Substrate Models for Co-Simulation of Power and Signal Integrity Proceedings Article In: IMAPS 42th International Symposium on Microelectronics and Packaging, San Jose, California, USA, November 3-5, 2009. |

In: Microwave and Optical Technology Letters, Bd. 51, Nr. 9, 2009. |

In: IEEE Transactions on Microwave Theory and Techniques, Bd. 57, Nr. 8, 2009. |

Differential to Common Mode Conversion Due to Asymmetric Ground Via Configurations Proceedings Article In: IEEE Workshop on Signal Propagation on Interconnects (SPI), Strasbourg, France, May 12-15, 2009. |

Extraction of Broadband Error Boxes for Microprobes and Recessed Probe Launches for Measurement of Printed Circuit Board Structures Proceedings Article In: IEEE Workshop on Signal Propagation on Interconnects (SPI), Strasbourg, France, May 12-15, 2009. |

Is 25 Gb/s On-Board Signaling Viable? Artikel In: IEEE Transactions on Advanced Packaging, Bd. 32, Nr. 2, 2009. |

Extraction of Via-Plate Capacitance of an Eccentric Via by an Integral Approximation Method Artikel In: IEEE Microwave and Wireless Components Letters, Bd. 19, Nr. 5, 2009. |

Bandwidth Study of Recessed Probe Launch Variations for Broadband Measurement of Embedded PCB Structures Proceedings Article In: German Microwave Conference (GeMic), Munich, Germany, March 16-18, 2009. |

Fully Analytical Methodology for Fast End-to-End Link Analysis on Complex Printed Circuit Boards including Signal and Power Integrity Effects. Proceedings Article In: IEC DesignCon Conference, Santa Clara, USA, February 2-5, 2009. |

Including Stripline Connections into Network Parameter Based Via Models for Fast Simulation of Interconnects Proceedings Article In: International Zurich Symposium on Electromagnetic Compatibility, Switzerland, January 12-15, 2009. |

The Viability of 25 Gb/s On-board Signaling Proceedings Article In: Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, May 27-30, 2008. |

Simulation of Via Interconnects Using Physics-Based Models and Microwave Network Parameters Proceedings Article In: IEEE Workshop on Signal Propagation on Interconnects (SPI), Avignon, France, May 12-15, 2008. |

Analysis and Optimization of the Recessed Probe Launch for High Frequency Measurements of PCB Interconnects Proceedings Article In: IEEE Design, Automation and Test in Europe Conference and Exhibition (DATE), Munich, Germany, March 10-14, 2008. |

Verkopplung einer schnellen PEEC-Methode mit der Momentenmethode bei gedruckten Schaltungen mittels der elektrischen Feldstärke Proceedings Article In: Internationale Fachmesse und Kongress für Elektromagnetische Verträglichkeit (EMV Düsseldorf), Düsseldorf, Germany, February 18-21, 2008. |