# CONMLS

# Institut für Theoretische Elektrotechnik

Technische Universität Hamburg (TUHH)

Copyright © 2014-2017 Institut für Theoretische Elektrotechnik, Technische Universität Hamburg, Harburger Schloss Str 20, D-21079 Hamburg, Germany For question and concerns regarding this document, please consult Torsten Reuschel (email: torsten.reuschel@tuhh.de).

WWW.TET.TUHH.DE

This book refers to CONMLS rev1096 with TETlib rev651. Features available in other versions may not be covered. Likewise, not all of the described features may be available in former revisions. The following authors contributed to this documentation: David Dahl, Sebastian Müller, Torsten Reuschel, and Renato Rimolo-Donadio.

Hamburg, Germany, September 6, 2017

# Contents

les l'e

| 1              |                                                                          | . 5      |

|----------------|--------------------------------------------------------------------------|----------|

| 2              | Installation                                                             | . 7      |

| 2.1            | Windows                                                                  | 7        |

| 2.1.1          | Installation of the CONCEPT-II MLS module under Windows operating system | s 7      |

| 2.1.2          | Installation of auxiliary software                                       |          |

| 2.1.3          | Test of the installation                                                 | . 8      |

| 3              | Getting Started                                                          | . 9      |

| 3.1            | Graphical User Interface                                                 | 9        |

| 3.1.1          | Example 1: Via-to-Via Link                                               | 10       |

| 3.1.2          | Example 2: Multilayer Thru Vias                                          | 20       |

| 3.1.3          | Example 3: Pin Field with 64 Vias                                        | 21       |

| 3.2            | Running from Command Line                                                | 22       |

| 4              | Technical Reference                                                      | 23       |

| 4.1            | Simulation Setup                                                         | 23       |

| 4.1.1          | Model Parameterization                                                   | 24       |

| 4.1.2          | Parameter Sweeping                                                       | 25       |

| 4.1.3          | Algorithm Configuration                                                  | 27       |

| 4.1.4          |                                                                          | 30       |

| 4.1.5<br>4.1.6 |                                                                          | 31<br>31 |

|                | Selection of Output Data                                                 |          |

| 4.2            | Specification of Board Geometry (2D) and Components                      | 32       |

| 4.2.1          |                                                                          | 34       |

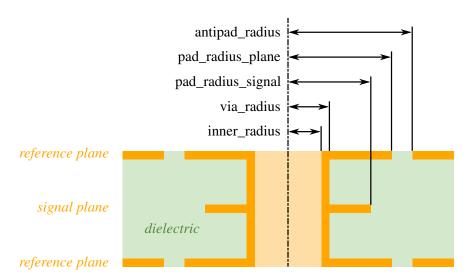

| 4.2.2<br>4.2.3 | Via Geometry and Modeling                                                | 35<br>39 |

| 4.2.3          |                                                                          | 39<br>40 |

| 4.2.4          | Microstrip Transmission Lines (untested)                                 | 40       |

| 4.2.6          | Multiconductor Transmission Lines                                        | 41       |

| 4.2.7          |                                                                          | 45       |

| 4.2.8          | Pads (untested)                                                          | 45       |

| 4.2.9          | Ports                                                                    | 45       |

Cap de

6

| 4.3 | 3 Stackup Geometry     |    |  |  |  |

|-----|------------------------|----|--|--|--|

| 4.4 | Material Specification | 48 |  |  |  |

| 5   |                        | 49 |  |  |  |

|     | Bibliography           | 51 |  |  |  |

# 1 — Introduction

The CONMLS code is the improved Fortran [1] implementation of the Matlab [2] Via Pin Simulator (VPF) code [3]. It makes use of the models discussed in [4, 5, 6, 7, 8] to simulate multilayer substrates enclosed by solid reference planes. This document explains the syntax, structure and functionality.

'e', 'e', 'e'

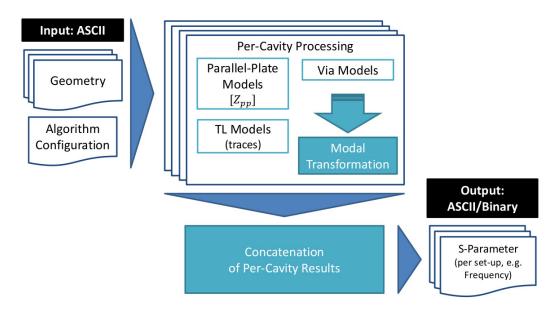

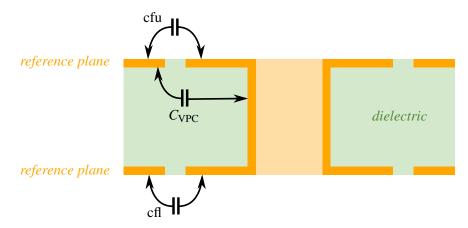

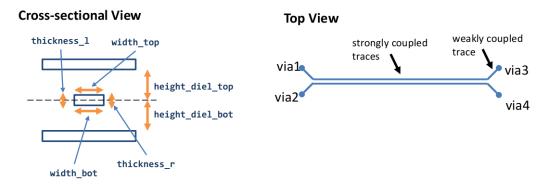

Figure 1.1 illustrates the program functionality and main building blocks. An interpreter reads the input files, which are a high-level description of the structure to be simulated. These files are then decoded. A second code component gets the variables created by the interpreter and identifies the cavities and their related interconnect elements. Then, the calculator computes the parallel-plate impedance per cavity, generates or imports the transmission line models for traces, and calculates or reads the via-to-plane capacitances to approximate the near fields in the antipad region. The calculator combines the plane and trace model by applying modal decomposition, and creates the interconnection matrices for via capacitances and lumped elements. Finally, the partial results are concatenated, for instance, using segmentation techniques. Post-processing functions and utilities are available to store (e.g. as lydite- or touchstone files [9]) and visualize the results. This version of the program is based on previous code developments [3, 10, 11, 12]. It has been interfaced with a revised CIM package [13] which allows the computation of arbitrary-shaped planes by applying the contour integral method. Another previously external algorithm for the computation of MTL systems with an hybrid 2D approach for arbitrary cross sections [14, 15] is included in the CONMLS code.

Figure 1.1: Flow chart of input/output and code functionalities in CONMLS.

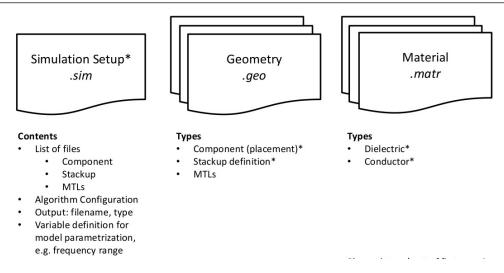

Figure 1.2: Input files for the high-level description of multilayer substrates in CONMLS are based on the widely used INI-format. Asterisks mark mandatory files. Other files may be required depending on the configuration of the algorithm.

Figure 1.2 shows the required input files and their dependencies. The fundamental configuration is provided through the simulation setup (.sim-file). The choice of algorithms and their respective parameters is contained in this file. Moreover, models may be freely parameterized with regard to variables and parameter sweeps, all of which are to be defined in the simulation setup. Additional files such as the geometry specification are linked. Geometry definition of PCB layout, stackup, vias, and multi-conductor transmission lines (MTLs) are to be provided through .geo-files. These files may utilize physical material definitions that are located in .matr-files.

# Notation

Parts of this user guide are enriched by one or more of the following elements:

- Remarks provide additional information for advanced users.

- Notes give hint to specifics in configuration and behavior of CONMLS.

Short examples of code and syntax are provided in the following way:

mlss.2.exe --help

The CONMLS code is available for Linux and Windows operating systems.

# 2.1 Windows

The following guide describes the installation process of CONMLS under MS Windows 64-bit and the steps required to get started:

# 2.1.1 Installation of the CONCEPT-II MLS module under Windows operating systems

- 1. Run *conmls-[xx]-setup.exe* to install the CONMLS binaries, where *[xx]* denotes the version.

- 2. Extend the system path by C:\CONMLS-1.0\bin or wherever the package has been installed, here referred to as \$CONMLS.

|                                                             | Hardware        | Erweitert                                                 | Completenskitz                                                         | Demetr                                    |       |

|-------------------------------------------------------------|-----------------|-----------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------|-------|

| nputername                                                  | Hardware        | Liwellen                                                  | Computerschutz                                                         | Remote                                    |       |

| mgebungsv                                                   | /ariablen       |                                                           |                                                                        |                                           | Σ     |

|                                                             |                 |                                                           |                                                                        |                                           |       |

| <u> </u>                                                    |                 |                                                           |                                                                        |                                           | _     |

| Benutzer                                                    | variable be     | arbeiten                                                  |                                                                        |                                           | ×     |

|                                                             |                 |                                                           |                                                                        |                                           |       |

| Name de                                                     | r Variablen:    | PATH                                                      |                                                                        |                                           |       |

|                                                             |                 |                                                           |                                                                        |                                           |       |

| Wert der Variablen: in;C:\CONMTLI-1.0\bin;C:\CONMLS-1.0\bin |                 |                                                           |                                                                        |                                           |       |

| OK Abbrechen                                                |                 |                                                           |                                                                        |                                           |       |

|                                                             |                 |                                                           | OK                                                                     | Abbre                                     | chen  |

|                                                             |                 |                                                           | ОК                                                                     | Abbre                                     | chen  |

|                                                             |                 |                                                           | ОК                                                                     | Abbre                                     | chen  |

| Systemvari                                                  | ablen           |                                                           | ОК                                                                     | Abbre                                     | chen  |

| Systemvari<br>Variable                                      |                 | Wert                                                      | OK                                                                     | Abbre                                     | chen  |

| Variable                                                    |                 |                                                           |                                                                        | ,                                         | chen  |

|                                                             |                 |                                                           | s\system32\cmd.ex                                                      | ,                                         | chen  |

| Variable<br>ComSpec<br>CONCEPT                              | : 1             | C: \Windows                                               | s\system32\cmd.ex                                                      | ie ie                                     |       |

| Variable<br>ComSpec<br>CONCEPT<br>F_EM64T                   | :<br>T<br>_REDI | C: \Windows<br>c: \concept-3<br>C: \Program               | s\system32\cmd.ex<br>II-12.0                                           | ie<br>n Files\In                          |       |

| Variable<br>ComSpec<br>CONCEPT<br>F_EM64T                   | :<br>T<br>_REDI | C: \Windows<br>c: \concept-<br>C: \Program<br>C: \Program | s\system32\cmd.ex<br>II-12.0<br>Files (x86)\Commo<br>Files (x86)\Commo | ie<br>on Files\In<br>on Files\In          | · · · |

| Variable<br>ComSpec<br>CONCEPT<br>F_EM64T                   | :<br>T<br>_REDI | C: \Windows<br>c: \concept-3<br>C: \Program               | s\system32\cmd.ex<br>II-12.0<br>Files (x86)\Commo                      | ie<br>n Files\In                          | · · · |

| Variable<br>ComSpec<br>CONCEPT<br>F_EM64T                   | :<br>T<br>_REDI | C: \Windows<br>c: \concept-<br>C: \Program<br>C: \Program | s\system32\cmd.ex<br>II-12.0<br>Files (x86)\Commo<br>Files (x86)\Commo | ie<br>on Files\In<br>on Files\In          | · · · |

| Variable<br>ComSpec<br>CONCEPT<br>F_EM64T                   | :<br>T<br>_REDI | C: \Windows<br>c: \concept-<br>C: \Program<br>C: \Program | s\system32\cmd.ex<br>II-12.0<br>Files (x86)\Commo<br>Files (x86)\Commo | ie<br>in Files\In<br>in Files\In<br>Lösch | · •   |

Figure 2.1: Setting the path to the CONMLS executables (System variables/Name of variables).

To do so, open the System applet in the Control panel (Systemsteuerung). Choose the

register Advanced (Erweitert). Click on Environment variables (Umgebungsvariable).

Select the entry *Path* of *System variables* (Systemvariablen) and press *Edit* (Bearbeiten). A window according to Fig. 2.1 opens where *Path* can be completed. Note: *Path* has to be extended by a semicolon followed by the CONMLS path. For details see Fig. 2.1.

The installation works only properly if all programs that are contained in the directory \$CONMLS/bin can be called without specifying the complete path. Please do not execute programs under \$CONMLS/bin. Copying of executables is not necessary and should not be done!

#### 2.1.2 Installation of auxiliary software

Gnuplot is necessary for the graphical representation of curves. To install it, download the binaries from http://www.gnuplot.info.

CONMLS uses the program gnuplot.exe. Please extend the variable PATH by the corresponding path, e.g., *C:\Programs\gnuplot\bin* or wherever gnuplot.exe is installed. The program must be callable from any working directory.

# 2.1.3 Test of the installation

Using a command line window, the following two steps can be used to validate that the path variables and binaries are configured and installed properly.

- (a) Type conmls.exe <Enter>. The GUI of CONMLS appears. If not, the Path has not been specified properly.

- (b) Type gnuplot.exe <Enter> at the command line. The gnuplot window appears. If not, the Path has not been specified properly.

This chapter gives some aid to those who are new to the CONMLS code.

# 3.1 Graphical User Interface

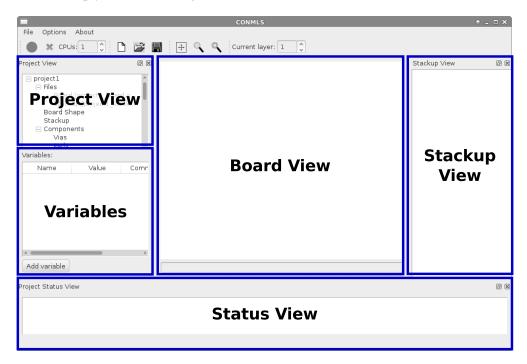

Starting the graphical user interface CONMLS for the first time, the various design views and monitors are empty as shown in Fig. 3.1.

Figure 3.1: Graphical user interface CONMLS after first startup.

The depicted views and monitors are:

Project View A tree-structured list of all components, models, and configurations.

**Board View** A bird's view of the PCB.

Stackup View The stackup of the PCB.

**Variables** A list of variables used in the current project. Variables can be utilized for parameter sweeping.

Status View The output of the backend is piped to this monitor.

**Toolbar** Direct access to repeatedly used functions such as loading and saving a project as well as running a simulation.

The following sections provide details on functionality and usage of the graphical user interface based on specific examples.

## 3.1.1 Example 1: Via-to-Via Link

The first example features two vias that are interconnected by a transmission line on layer *signal1*. One of the vias ranges through the entire stackup and features a via stub. The second via is back-drilled and ends on layer *signal1*.

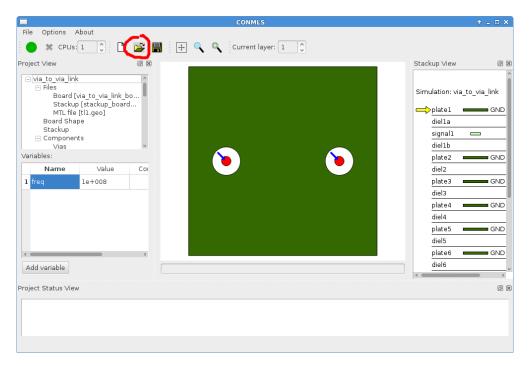

Loading a previously stored project can be done using the *File* menu or using the *Open file*.. button in the toolbar, cf. Fig. 3.2.

Figure 3.2: Graphical user interface CONMLS after loading example Via-to-Via Link.

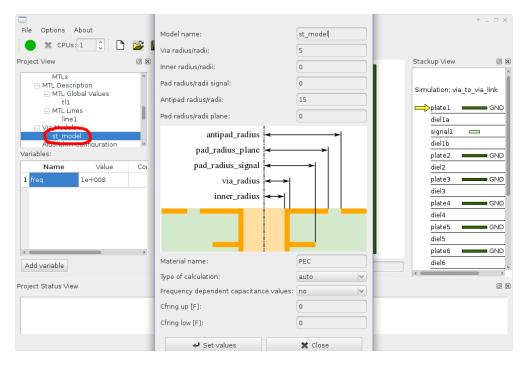

All properties and settings of the project are accessible through the project tree on the left of the screen. Typically, materials need imported or defined prior to setting up the stackup, cf. Fig. 3.3. The shape of the board and the layers of the stackup can be configured as depicted in Figs. 3.4 and 3.5. Next, the via models can be defined as shown in Fig. 3.6. Once defined, vias can be placed as shown in Fig. 3.7.

Note how the via *via1* ranges from top to bottom of the board. The graphical preview of the geometry offers two more perspectives. Clicking on the white antipad area of a via opens the cross-sectional view as shown in Fig. 3.8. Second, the currently displayed layer can be selected in the stackup view on the right, cf. Fig. 3.9. Selecting the layer plate2 reveals how only *via1* pinches through this metallic layer.

Ideal transmission lines as well as generic multiconductor transmission lines can be used to interconnect vias. Figures 3.10 and 3.11 depict the latter. Again, selecting the corresponding layer, here: *signal2*, reveals the routing of transmission lines, cf. Fig. 3.12.

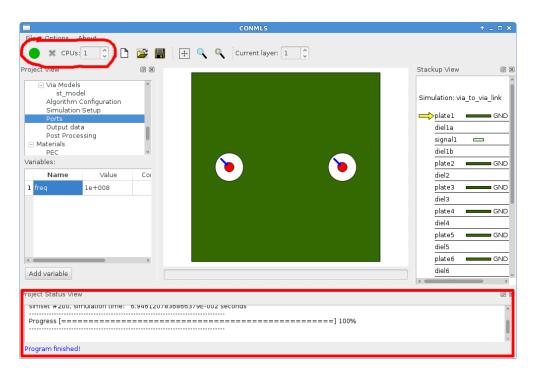

Once the geometry is set up, the algorithms, models, and boundary conditions that are to be used for the simulation can be configured as depicted in Fig. 3.13. Sweeping parameters such as the frequency can be selected from the project tree, cf. Fig. 3.14. Finally, ports should be placed as shown in Fig. 3.15 in order to probe the geometry which is to be simulated.

Finally, the simulation can be started after selecting the number of processors to be used.

| File Options About                                                                           | + 🔍 🔍 Current layer: 1 🗘                                                                                                                                                                                                                |                                                                                  |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Project View © 🗹<br>Simulation Setup<br>Ports<br>Output data<br>Post Processing<br>Materials | CONMLS - Material Description 🔶 🗆 X<br>Material Specification                                                                                                                                                                           | Stackup View<br>Simulation: via_to_via_link<br>→ plate1 GND<br>diel1a<br>signal1 |

| Plots<br>Variables:                                                                          | Material name: FR-4 <br>Material type: dielectric V                                                                                                                                                                                     | diel1b<br>plate2 GND                                                             |

| Name     Value     Cor       1     freq     1e+008                                           | Conductivity:<br>Relative permeability:<br>Relative permittivity:<br>Dielectric loss tangent:<br>Dielectric loss tangent:<br>Dielectric loss tangent:<br>Dielectric loss tangent:<br>Dielectric loss tangent:<br>Cose<br>Close<br>Close | diel2<br>plate3 GND<br>diel3<br>plate4 GND<br>diel4<br>plate5 GND<br>diel5       |

| Add variable                                                                                 |                                                                                                                                                                                                                                         | plate6 GND<br>diel6                                                              |

|                                                                                              |                                                                                                                                                                                                                                         |                                                                                  |

Figure 3.3: Editing a material definition.

CONMLS offers parallelization based on OpenMP (shared memory parallelization). Completion of the simulation is indicated by a blue *Program finished!* at the bottom of the project status view. For quick sanity checks of the results, the graphical user interface offers selecting input and output ports and viewing the magnitude of their respective transfer function, cf. Figs. 3.17 through 3.19.

| File   | Options About          |            | CO         | NMLS           |                     |       |                    | ↑ _ □ ×   |

|--------|------------------------|------------|------------|----------------|---------------------|-------|--------------------|-----------|

|        | 🗶 CPUs: 1 🗘 🗋          | 🚔 📕 🕂      | 🔍 🔍 Curr   | ent layer: 1   | \$                  |       |                    |           |

| Projec | t View                 |            |            |                |                     |       | Stackup View       | ØX        |

|        | Stackup [stackup_board |            | CONMLS - S | hape Descripti | on                  | ↑ □ × |                    | Â         |

|        | Board Shape<br>Stackup |            | Shap       | pe Description | n                   |       | Simulation: via_to | _via_link |

| e      | Components             | rect       |            |                |                     | ~     |                    | GND       |

|        | Vias<br>Pads           | Maniaianum | N          | March Inc.     | Ar an an discussion |       | diel1a             |           |

|        | Lumped Elements        | X minimum  | X maximum  | Y minimum      | Y maximum           |       |                    |           |

| Varia  | TL (ideal)             | 1 0        | 200        | 0              | 200                 |       | diel1b             |           |

| varia  | Name Value             |            |            |                |                     |       | plate2 💻<br>diel2  | GND       |

| 1 fre  |                        |            |            |                |                     |       |                    | GND       |

| 1 10   | ed Te+008              |            |            |                |                     |       | diel3              | GND       |

|        |                        |            |            |                |                     |       |                    | GND       |

|        |                        |            |            |                |                     |       | diel4              | GND       |

|        |                        |            |            |                |                     |       |                    | GND       |

|        |                        |            |            |                |                     |       | diel5              |           |

|        |                        |            |            |                |                     |       |                    | GND       |

|        | l variable             |            |            |                |                     |       | diel6              |           |

| Add    | I Variable             | و لم       | Set values |                | 🗶 Close             |       | <                  | >         |

| Projec | t Status View          |            |            |                |                     |       |                    | 0 X       |

|        |                        |            |            |                |                     |       |                    |           |

Figure 3.4: Editing the shape of the printed circuit board.

|                                                              | ð X |                 |                        | _                              | _         |            | Stackup View      | ß          |

|--------------------------------------------------------------|-----|-----------------|------------------------|--------------------------------|-----------|------------|-------------------|------------|

| ∃ via_to_via_link<br>⊡ Files<br>Board [via_to_via_link_bo    |     |                 | CONMLS - Sta<br>Stacku | ckup Descript<br>up Descriptic |           | + = ×      | Simulation: via_t | o_via_link |

| Stackup [stackup_board.<br>MTL file [tl1.geo]<br>Beard Shape |     | ts for stackup: | mil                    | <b>v</b>                       |           |            | diella            | GNE        |

| Stackup                                                      |     | Label           | Connectivity           | Material                       | Thickness | Тур        | signal1           |            |

| <ul> <li>Components</li> <li>Vias</li> </ul>                 | 1   | plate1          | GND                    | PEC                            | 1         | plane      | diel1b            |            |

| ariables:                                                    | 2   | diella          |                        | FR-4                           | 5.5       | dielectric | plate2 💻          | GNE        |

| Name Value                                                   | 3   | signal 1        | SL1                    | PEC                            | 1         | signal     | diel2             |            |

| freq 1e+008                                                  | 4   | diel1b          |                        | FR-4                           | 5.5       | dielectric | plate3 💻<br>diel3 | GN         |

|                                                              | 5   | plate2          | GND                    | PEC                            | 1         | plane      |                   | GNI        |

|                                                              | < ( |                 |                        |                                |           |            | diel4             |            |

|                                                              |     |                 |                        |                                |           |            | plate5 💻          | GN         |

|                                                              | A   | ppend 🗸 Tota    | I numbers              | *                              | 0         | 🗸 Ok       | diel5             |            |

|                                                              |     |                 |                        |                                |           |            | plate6 💻          | GNE        |

| Add variable                                                 |     | s له            | iet values             |                                | 🗙 Close   |            | diel6             |            |

|                                                              | 252 |                 |                        |                                |           |            |                   | <br>[7     |

Figure 3.5: Editing the layers of the stackup.

Figure 3.6: Definition of a via model.

| File (    | Opti | ions About                       |            |               | CON          | MLS            |            |             |             | ÷.                   | ×                 |

|-----------|------|----------------------------------|------------|---------------|--------------|----------------|------------|-------------|-------------|----------------------|-------------------|

|           | ×    | CPUs: 1                          | 🗋 🗋 🚔      | <b>  </b> + ( | 🔍 🔍 Currer   | nt layer: 1    |            |             |             |                      |                   |

| Project \ | √iev | v                                | 6          | ×             |              |                |            |             | Stackup Vie | w                    | ß×                |

|           | ζ    | ckup<br>up nents<br>Vias<br>au b | nte l      |               |              |                |            |             | Simulation  | via_to_via_<br>• • × |                   |

|           |      |                                  |            |               |              | ia Description |            |             |             | TUA                  | н                 |

| -         |      |                                  |            |               |              |                |            |             |             |                      |                   |

| Variab    |      | Label                            | Туре       | Model         | Connectivity | X position     | Y position | Start layer | End layer   | Start dej            | GND               |

|           | 1    | vial                             | blind      | ✓ st_model    | SL1          | 40             | 100        | plate1      | platell     |                      | ы                 |

| 1 fre     | 2    | via2                             | blind      | ✓ st_model    | SL1          | 160            | 100        | plate1      | signal1     |                      | GND               |

|           |      |                                  |            |               |              |                |            |             |             |                      | <u>3ND</u><br>3ND |

| ۲ مطا     | <    | Append                           | ► Total nu | Imbers        | 1            | ~              | 0          |             | × ×         | »<br>Dk              | 3ND<br>           |

| Project   |      |                                  | به         | Set values    |              |                |            | 🗶 Close     |             |                      | 0 8               |

|           |      |                                  |            |               |              |                |            |             |             | -                    |                   |

Figure 3.7: Placement of vias.

|              | MLSS - Model                                          | ↑ _ □ × |

|--------------|-------------------------------------------------------|---------|

| <u>F</u> ile |                                                       |         |

|              |                                                       |         |

|              | via1, model: st_model                                 |         |

|              |                                                       |         |

|              | plate1_size: 1 mil                                    |         |

|              | diella size: 5,5 mil<br>signal1_size: 1 mil           |         |

|              | di <u>ěl 1b. size: 5.5 mil</u><br>plate2. size: 1 mil |         |

|              | diel2 size: 12 mil                                    |         |

|              | plate3 size: 1 mil                                    |         |

|              | diel3 size: 12 mil                                    |         |

|              | plate4 size: 1 mil                                    |         |

|              | diel4 size: 12 mil                                    |         |

|              | plate5 size: 1 mil                                    |         |

|              | diel5 size: 12 mil                                    |         |

|              | plate6 size: 1 mil                                    |         |

|              | diel6 size: 12 mil                                    |         |

|              | plate7 size: 1 mil                                    |         |

|              | diel7 size: 12 mil                                    |         |

|              | plate8 size: 1 mil                                    |         |

|              | diel8 size: 12 mil                                    |         |

|              | plate9 size: 1 mil                                    |         |

|              | diel9 size: 12 mil                                    |         |

|              | plate10 size: 1 mil                                   |         |

|              | diel10 size: 12 mil                                   |         |

|              | plateri size: i mi                                    |         |

|              |                                                       |         |

|              |                                                       |         |

|              |                                                       |         |

Figure 3.8: Cross-sectional view of via via1.

| <ul> <li>via_to_via_link</li> <li>Files</li> <li>Board (via_to_via_link_bc)</li> <li>Stackup (stackup_board)</li> <li>Board Shape</li> <li>Stackup 2</li> <li>Components</li> <li>Vias</li> <li>Variables:</li> <li>Name Value Coi</li> <li>I freq 1e+008</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CONMLS + _ 🗆 X                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Project View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |

| • via to, via link       • Files       Simulation: via_to_via_link         Board (via_to_via_link_bo)       • Simulation: via_to_via_link         • Mth.file(11.geo)       • Board Shape         • Board Shape       • If the signal is in the s | 🚰 📕 🕂 🔍 Current layer: 5 🛟                           |

| Files       Board (via to_via link bo)         Stackup [stackup board       Image: stackup board         Mrt file (l1.geo)       Board Shape         Board Shape       Simulation: via_to_via_link         Stackup       Components         Variables:       Image: stackup         Image: freq       1e+008         Image: freq       1e+008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ම 🕱 Stackup View ම ව                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Cor<br>Cor<br>Cor<br>Cor<br>Cor<br>Cor<br>Cor<br>Cor |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                      |

Figure 3.9: Selecting and viewing the layout of layers in the stackup.

| Project View<br>MTLs<br>MTL Description | CONMLS                                                                                                                                                                                                                                                                   |                                                                                                                                                         | Stackup View 🕑 🗷                                                                                                                |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| MT_ Global Values                       | CONMLS - MTL GLOBA<br>Values for Multiconductor<br>MTL name:<br>Choice of algorithm:<br>Reference to material of conductor:<br>Reference to material of dielectric:<br>Coupling factor, lower limit:<br>Minimum relative deviation of two geometry points<br>Line names: | Transmission Lines          [t]1         [Classical 2D-MTL algorithm, optimized]         [PEC        v]         [FR-4        v]         [0.01       [v] | plate 1 GND<br>diel 1a<br>signal 1 GND<br>diel 2 GND<br>diel 2<br>plate 3 GND<br>diel 3<br>plate 4 GND<br>diel 4<br>plate 5 GND |

| Add variable<br>Project Status View     | <b>₽</b> Save                                                                                                                                                                                                                                                            | 🗶 Close                                                                                                                                                 | diel5<br>plate6 GND<br>diel6 8                                                                                                  |

Figure 3.10: Definition of a multiconductor transmission line (MTL) object.

| C.                                                             | CONML                          | S - MTL Line VALUES              | ↑ □ × | ŕ                      | ×     |

|----------------------------------------------------------------|--------------------------------|----------------------------------|-------|------------------------|-------|

| File Options About                                             | Description of a               | multiconductor transmission line |       |                        |       |

| Project View                                                   | Identifier of line:            | line 1                           |       | Stackup View           | ð×    |

| MTLs                                                           | Units:                         | mil                              | ~     |                        | î     |

| <ul> <li>MTL Description</li> <li>MTL Global Values</li> </ul> | Width of trace:                | 4                                |       | Simulation: via_to_via | _link |

| tl1<br>- MT- times                                             | Thickness of trace:            | 1                                |       | plate1                 | GND   |

| line1                                                          | Height of dielectric at top:   | 5.5                              |       | diel1a                 | _     |

| st_model                                                       | Height of dielectric at bottom |                                  |       | signal1 📼              |       |

| Algorithm Configuration                                        | -                              |                                  |       | diel1b                 |       |

|                                                                | Trace position:                | up                               | ~     | plate2                 | GND   |

|                                                                | Trace coordinates:             |                                  |       | diel2                  |       |

| 1 freq 1e+008                                                  | X Y                            |                                  |       | plate3 diel3           | GND   |

|                                                                | 1 40 100                       |                                  |       | plate4                 |       |

|                                                                | 2 160 100                      |                                  |       | diel4                  | GND   |

|                                                                |                                |                                  |       | plate5                 |       |

|                                                                |                                |                                  |       | diel5                  | GND   |

|                                                                |                                |                                  |       | plate6                 |       |

|                                                                |                                |                                  |       | diel6                  | GND   |

| Add variable                                                   |                                |                                  |       | dielo                  | v     |

| Project Status View                                            |                                |                                  |       |                        | ØX    |

|                                                                | Append V Total numbers         |                                  | Ok    |                        |       |

|                                                                |                                |                                  |       |                        |       |

|                                                                | 🖊 Save                         | 🗶 Close                          |       |                        |       |

|                                                                |                                |                                  |       |                        |       |

|                                                                |                                |                                  |       |                        |       |

Figure 3.11: Editing the traces ('lines') of a multiconductor transmission line object.

|                                                                                                                                                                                                                    |           | CONMLS                 | ↑ _ □ ×                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|------------------------------------------------------------------------------------------|

| File Options About                                                                                                                                                                                                 |           |                        |                                                                                          |

| 🔴 💥 CPUs: 1                                                                                                                                                                                                        | े 🗅 😅 📕   | 🕂 🔍 Current layer: 3 🛟 |                                                                                          |

| Project View                                                                                                                                                                                                       | o x       |                        | Stackup View 🛛 🕅                                                                         |

| <ul> <li>via_to_via_link</li> <li>Files</li> <li>Board [via_to_<br/>Stackup [stac</li> <li>MTL file [tll.ge</li> <li>Board Shape</li> <li>Stackup</li> <li>Components</li> <li>Vias</li> <li>Variables:</li> </ul> | kup_board |                        | Simulation: via_to_via_link<br>plate1 GND<br>diel1a<br>diel1b<br>plate2 GND              |

| Name                                                                                                                                                                                                               | Value Coi |                        | diel2                                                                                    |

| 1 freq 1e+0                                                                                                                                                                                                        |           |                        | plate3 GND<br>diel3<br>plate4 GND<br>diel4<br>plate5 GND<br>diel5<br>plate6 GND<br>diel6 |

| Project Status View                                                                                                                                                                                                |           |                        | S 8                                                                                      |

Figure 3.12: Signal layers can be selected from the stackup view to view the routing of traces.

| Project View                                                                   | ð X | _    |                                 |             |       | Stackup View       | ØX         |

|--------------------------------------------------------------------------------|-----|------|---------------------------------|-------------|-------|--------------------|------------|

| Via Models  Algorithm Configuration Completion Configuration Ports Output data |     | F    | CONMLS - Algor<br>Algorithm Cor |             | ↑ □ X | Simulation: via_to | o_via_link |

| Post Processing                                                                |     |      | Name                            | Value       | -     |                    |            |

| <ul> <li>Materials</li> <li>PEC</li> </ul>                                     |     | 1    | airap_top_bot                   | no          |       | diel1b             |            |

| Variables:                                                                     |     | 2    | autoseg_parameter               | S-parameter | ~     | plate2 💻           | GND        |

| Name Value                                                                     | Coi | 3    | bc                              | РМС         | ~     | diel2              |            |

| 1 freq le+008                                                                  |     | 4    | boundary parameter              | S-parameter |       |                    | GND        |

|                                                                                |     |      |                                 |             |       | diel3              |            |

|                                                                                |     | 5    | coax_ext                        | 0.          | _     |                    | GND        |

|                                                                                |     | 6    | rnax ext all                    | VAS         | v v   | diel4              |            |

|                                                                                |     | De   | efault values                   |             |       |                    | GND        |

|                                                                                |     |      |                                 |             |       | diel5              |            |

| <                                                                              | 2   |      | ✓ Save                          | 🗶 Close     |       |                    | GND        |

| Add variable                                                                   | x=  | 27.3 |                                 |             |       | <br>diel6          |            |

|                                                                                |     |      |                                 |             |       |                    |            |

| Project Status View                                                            |     |      |                                 |             |       |                    | đ×         |

|                                                                                |     |      |                                 |             |       |                    |            |

Figure 3.13: Selecting and configuring algorithms, e.g., semi-analytical models.

| File Options About                         |         | CON    | MLS          |                 |          |              | ↑ _ □ X  |

|--------------------------------------------|---------|--------|--------------|-----------------|----------|--------------|----------|

| 🔴 🗶 CPUs: 1 🗘 🎦                            | ጅ 📳 🕂 🔍 | Currer | nt layer: 1  |                 |          |              |          |

| Project View                               | 0 *     |        |              |                 | _        | Stackup View | 0 ×      |

| 🗆 Via Models                               | ^       |        |              |                 |          |              | - î      |

| st_model                                   |         |        | CONML        | S - Parameter S | Sweeping | <b>•</b>     | 🗆 🗙 link |

| Simulation Setup                           |         |        | I            | Parameter Sw    | veeping  |              | GND      |

| Output data<br>Post Processing             |         | Name   | Start        | Stop            | Steps    | Type         |          |

| Materials     PEC                          |         | 1 freq | le+008       | 2e+010          | 200      | linear 🗸     |          |

| Variables:                                 | Col     |        |              |                 |          |              | GND      |

| Name     Value       1     freq     1e+008 |         |        |              |                 |          |              | GND      |

|                                            |         |        |              |                 |          |              | GND      |

|                                            |         | freq   | <b>v</b> ]   | Refresh         |          | Add Sweep    | GND      |

| <                                          | 2       |        | ✔ Set values |                 | ,        | Close        | GND      |

| Add variable                               |         |        |              |                 |          |              | v        |

| Project Status View                        |         |        |              |                 |          |              | 0 ×      |

|                                            |         |        |              |                 |          |              |          |

|                                            |         |        |              |                 |          |              |          |

|                                            |         |        |              |                 |          |              |          |

| Add variable                               | 3       |        | Set values   |                 | 3        | ( Close      | v        |

Figure 3.14: Definition of parameter sweeps.

|                           |               | 01 |             |                |                    |    |       |           | Stackup View      | Ø          |

|---------------------------|---------------|----|-------------|----------------|--------------------|----|-------|-----------|-------------------|------------|

| ⊡ Via Models<br>st mod    |               |    |             | CONMLS         | - Port Description | on |       | ÷         | □ ×               |            |

| Algorithm (<br>Cimulation | Configuration |    |             | P              | ort descriptior    | ١  |       |           | lation: via_t     | o_via_link |

| Ports<br>Output dat       |               | Г  | Port label  | ∨ia label      | Type               |    | Side  | Impedance | diel1a            |            |

| Post Proce<br>Materials   | ssing         | 1  | pl          | vial           | single ende 🗸      | up | V     | 50        | signal1           |            |

| PEC                       |               | 2  | p2          | via2           | single ende 🗸      | up |       | 50        | diel 1b           |            |

| ariables:                 |               | F  | -           |                | []                 |    |       | J,        |                   | GN         |

| Name                      | Value         |    |             |                |                    |    |       |           | diel2             |            |

| freq                      | le+008        |    |             |                |                    |    |       |           |                   | GN         |

|                           |               |    |             |                |                    |    |       |           | diel3             |            |

|                           |               |    |             |                |                    |    |       |           |                   | GN         |

|                           |               |    |             |                |                    |    |       |           | diel4             |            |

|                           |               | ł  | Append 🗸 To | otal numbers 1 | <b>^</b>           |    | 0     | 🔹 🗸 Ok    | plate5 💻<br>diel5 | GN         |

|                           |               |    |             |                |                    |    |       |           |                   |            |

|                           | _             |    |             | Set values     |                    |    | 🗶 Clo | se        | plate6 💻<br>diel6 | GN         |

| Add variable              |               |    |             |                |                    |    |       |           | dielo             | _          |

| ject Status View          |               |    |             |                |                    |    |       |           |                   | (i         |

Figure 3.15: Definition of ports, e.g., via ports and stripline ports.

Figure 3.16: Setting the number of processors to be used (shared memory parallelization).

| File Options About                                                     | CONMLS Post Processing                                 | ↑ _ □ X                                    |

|------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------|

| 🔵 🗶 CPUs: 1 🛟 🗋 😂 📕                                                    | Select values for view with gnuplot                    |                                            |

| Project View                                                           | Sweep Selection                                        | Stackup View 🛛 🖉                           |

| Simulation Setup<br>Ports<br>Potput data                               | Sweep name     eep/Step num       1     freq     sweep | Simulation: via_to_via_link                |

| Post Processing<br>Materials<br>PEC<br>FR-4                            |                                                        | →plate1 → GND<br>diel1a<br>signal1 →       |

| Plots<br>Variables:                                                    |                                                        | diel1b<br>plate2 GND                       |

| Name         Value         Col           1         freq         1e+008 | Gnuplot file: via_to_via_link_out.asc                  | diel2<br>plate3 GND<br>diel3<br>plate4 GND |

|                                                                        | Input port     Output port       1     1               | diel4<br>plate5 GND<br>diel5               |

| Add variable                                                           |                                                        | diel6                                      |

| Project Status View                                                    |                                                        | 0 8                                        |

| Progress [===================================                          | ☐ S parameter in dB<br>Select values ★ Close           | Û                                          |

| Program finished!                                                      |                                                        |                                            |

Figure 3.17: Selection of input and output ports for plotting.

| Gnuplot front-end<br>File Options Ratapprox |        | me/tetr/Softwa | re/mlss- | v2-dev/examp    | les/archive/SIMPLE/Via | _to_via_link | Ϋ́ΟΧ    |

|---------------------------------------------|--------|----------------|----------|-----------------|------------------------|--------------|---------|

|                                             |        | GNUPLOT        | FRONT    | FEND FOR C      | ONCEPT-II              |              |         |

| Title: via_to_via_link                      |        |                |          |                 |                        |              |         |

| X label: freq                               |        |                |          |                 |                        |              |         |

| Y label:                                    |        |                |          |                 |                        |              |         |

| Z label:                                    |        |                |          |                 |                        |              |         |

| Legend position:                            |        | right top      |          |                 |                        | <b>\</b>     |         |

| Number of files                             |        | 1              | Get data | file(s) 🗆 🗆 U   | Jse rel. path Refresh  | n info(s)    |         |

| File name                                   | Take   | Style          | Width    | Color           | Legend title           | Using        | Delet   |

| 1 via_to_via_link_out                       |        | Lines 🗸        |          | red 🗸           | s12, magnitude         | 1:4          | Delete  |

|                                             |        |                | 1        |                 | 1                      |              |         |

|                                             |        |                |          |                 |                        |              |         |

|                                             |        |                |          |                 |                        |              |         |

|                                             |        |                |          |                 |                        |              |         |

| Output to: Gnuplot View                     |        | Settings       | Output   | t file D File p | ame:                   |              | ø<br>g∨ |

| Output to. Onuplot view                     | 1.     | Settings       | outpu    |                 |                        |              | gv      |

| P                                           | ın gnı | uplot          |          |                 | 🚫 Cancel               |              |         |

|                                             | argni  | aproc          |          |                 | Gancer                 |              |         |

|                                             |        |                |          |                 |                        |              |         |

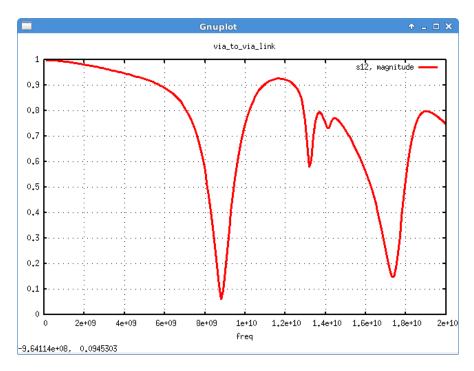

Figure 3.18: The plotting interface. Data may be imported from CONMLS as well as external files. Plots such as Fig. 3.19 can be displayed by clicking on *Run gnuplot*.

Figure 3.19: Transmission of the via-to-via link. The stub causes resonances near 9 GHz and 18 GHz.

# 3.1.2 Example 2: Multilayer Thru Vias

This example features two adjacent vias and can be used to investigate the crosstalk behavior in a multilayer board environment.

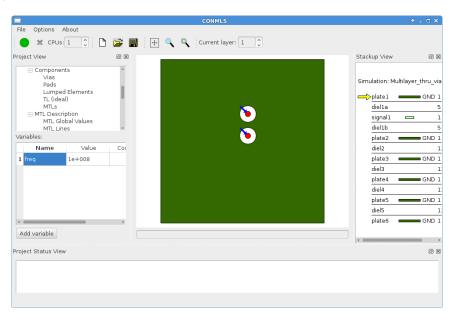

Figure 3.20: Main window view of demo scenario 2: two adjacent vias in a multilayer environment.

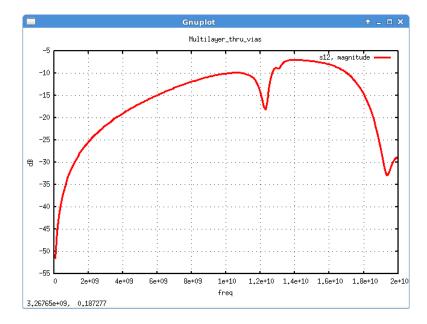

Figure 3.21: Crosstalk of two adjacent vias in a multilayer environment.

# 3.1.3 Example 3: Pin Field with 64 Vias

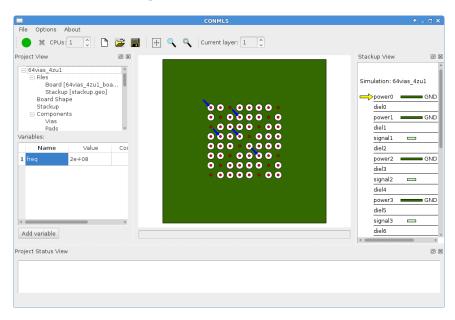

To demonstrate the efficiency of the CONMLS code, this example features a via pin field with 64 vias. On a standard office computer, this

Figure 3.22: Main window view of demo scenario 3: a pin field with 64 vias.

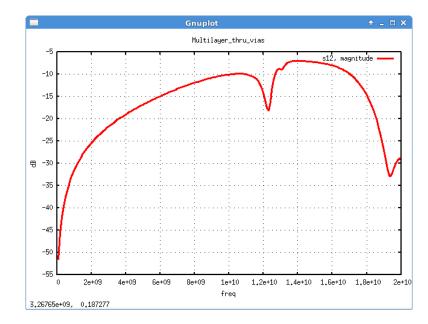

Figure 3.23: Crosstalk between the edge via and a central via of the pin field.

# **3.2** Running from Command Line

CONMLS allows for parallelization of computations based on *OpenMP*, a shared memory parallelization scheme. To utilize it, run CONMLS using the command

OMP\_NUM\_THREADS=[num] mlss.2 path/to/config.sim

where *num* sets the number of parallel threads during runtime. A corresponding input argument is available to set the desired number of threads:

```

mlss.2 -n [NUM_THREADS] path/to/config.sim

```

Note that this argument will override the conventional setting through the environment variable *OMP\_NUM\_THREADS*.

If parallelization is to be disabled, CONMLS needs to be explicitly configured to use only one process, e.g.

OMP\_NUM\_THREADS=1 mlss.2 path/to/config.sim

or

```

mlss.2 -n 1 path/to/config.sim

```

22

This chapter introduces the syntax used to configure CONMLS and build models. All files are based on the INI-format implementation available from *TETlib*. The INI-format arranges *attributes* and their respective *values* by means of *sections*:

```

1 [section]

2 #comment

3 attribute = value

```

() While the maximum line length is limited to 1024 characters as of TETlib rev589, whitespaces are automatically discarded and can be used for formatting purposes. Nevertheless, tabs are known to cause issues during processing by the Fortran code and should be avoided.

The input of CONMLS is structured into a algorithm configuration (.sim) and a physical description of the problem consisting of geometry (.geo) and material (.matr) definition, cf. Fig. 1.1. The details and contents of these files are discussed in the following.

# 4.1 Simulation Setup

The simulation setup file (file-extension .sim) is the principal file which is processed by CONMLS. Selection and configuration of algorithms as well as other global runtime options is achieved through this file. If an option is not defined, the program will used a default value. A warning is be issued and printed in the simulation log regarding the selection of a default value. The general structure of a simulation setup is given in Listing 4.1.

The identifier in the *global* section is required for ease of clarity as this type of file may be processed by other software packages that are being developed at the Institute of Electromagnetic Theory. The other sections are (in alphabetical order):

cim\_config This section is specific to the CIM [16] algorithm.

files Referencing of other project files, e.g. geometry definitions. One section only.

global System commands, to be used for control of software environment only. One section.

**output** Configuration of desired output, e.g. output filename and numerical precision of results. One section only.

parameter Selection and configuration of algorithm options. One section only.

sweep Definition of parameter sweep. Multiple instances of this section are allowed.

variables Definition of variables. One section only.

The actual positioning and order of results and attribute definitions in the file is irrelevant to the output of CONMLS and can be chosen ad libitum. However, note that the relative order of

```

Listing 4.1: Generic Simulation Setup File (.sim)

1 [global]

2 # simulation configuration file for mlss.2

3 identifier = mlss.2

4

5 [variables]

• myvar

7 my_2nd_Var

*

= 30e-9 * sin(pi/5)

= .5 * $myVar$

8

9 [sweep]

10 # name of the variable to be swept

11 name = freq

12 start

= 1e8

= 4e10

13 stop

= 400

15 # possible sweep types: linear, log

= linear

16 type

17

18 [files]

19 geometry

20 stackup

= 2d_board_definition.geo

= stackup_definition.geo

21 mtl

= mtl_definition.geo

22

23 [parameter]

24 autoseg_parameter = 1

25 boundary_parameter = 1

26bc= PMC27frequency= $freq$28method_zpp= crm_single29modesm000

28 meest

= 300

= 300

31

32 [output]

33 append

= 1

34 format

= lydite

35 # Output filename. If append==0, this is used as prefix and "_###"

36 # is added to the individual filenames where "###" denotes the

37 # simset index.

38 filename

= output_basename

39 precision

= double

```

multiple parameter sweep definitions will impact their delineation through CONMLS and as such will impact the automatic indexing on output.

All input will be turned to lower-case letters. This is particularly worth noting, because actual filenames need to be spelled using lower-case letters.

# 4.1.1 Model Parameterization

CONMLS allows for model parameterization by means of variables that can be used as placeholder for constant values as well as parameter sweeps, cf. subsequent section. Declaration and initialization of variables is achieved by means of simple attribute-value pairs in the *variables* section: Variables are available and may be used for the assignment of values throughout

```

1 [variables]

2 # declare a frequency value of 20GHz

3 freq = 20e9

4 # yet another arbitrary value

5 pitch_new = 10

```